Question: problem 2: Risc V singel cycle processor: Simplify the datapath of the single cycle RISC-V processor if it needed to support SUB and LW instructions

problem 2:

Risc V singel cycle processor:

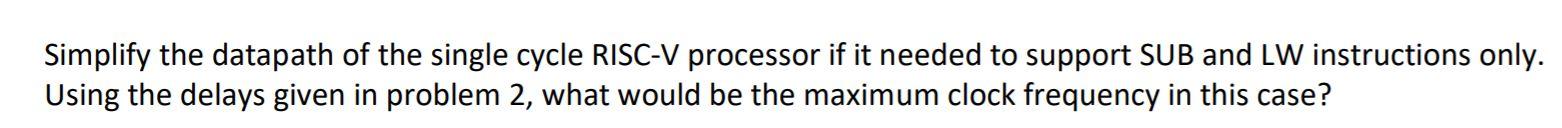

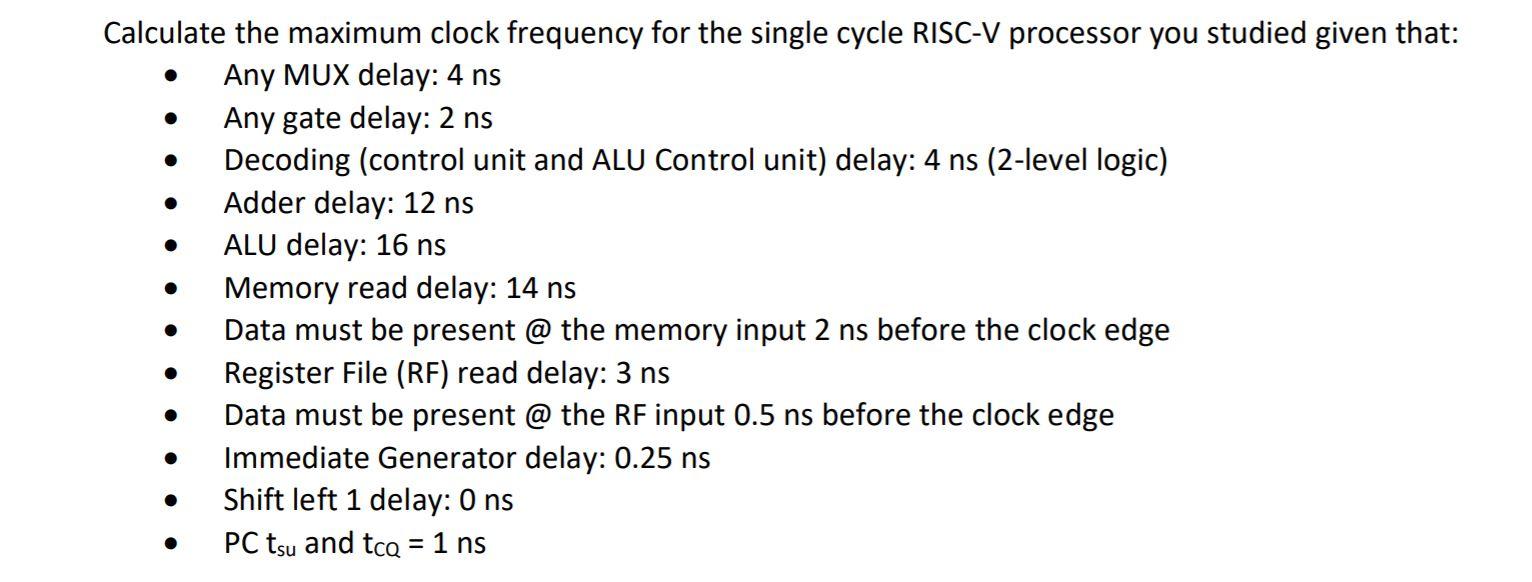

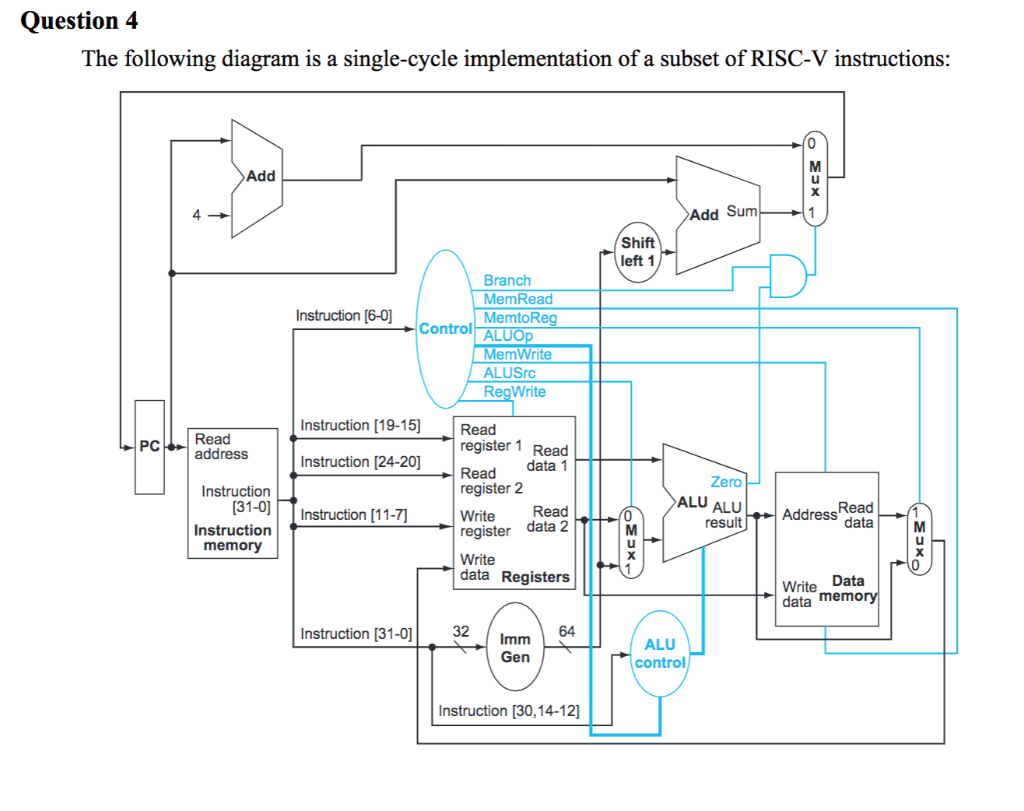

Simplify the datapath of the single cycle RISC-V processor if it needed to support SUB and LW instructions only. Using the delays given in problem 2, what would be the maximum clock frequency in this case? . Calculate the maximum clock frequency for the single cycle RISC-V processor you studied given that: Any MUX delay: 4 ns Any gate delay: 2 ns Decoding (control unit and ALU Control unit) delay: 4 ns (2-level logic) Adder delay: 12 ns ALU delay: 16 ns Memory read delay: 14 ns Data must be present @ the memory input 2 ns before the clock edge Register File (RF) read delay: 3 ns Data must be present @ the RF input 0.5 ns before the clock edge Immediate Generator delay: 0.25 ns Shift left 1 delay: Ons PC tsu and tca = 1 ns Question 4 The following diagram is a single-cycle implementation of a subset of RISC-V instructions: Add x3 4 Add Sum Shift left 1 Branch MemRead MemtoReg Instruction [6-O] Control ALUOP MemWrite ALUSrc RegWrite Instruction (19-15] Read PC Read address register 1 Read Instruction (24-20] Zero ALU ALU Instruction (31-0) Instruction memory Instruction (11-7] Read data 1 register 2 Write Read register data 2 Write data Registers result Address Read data 68sx, ES Write Data data memory Instruction (31-0) 32 64 Imm Gen ALU control Instruction (30,14-12]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts