Question: Problem 4 (20 points) We want to design a combinational circuit that detects the number of trailing I's and shifts these I's out. The input

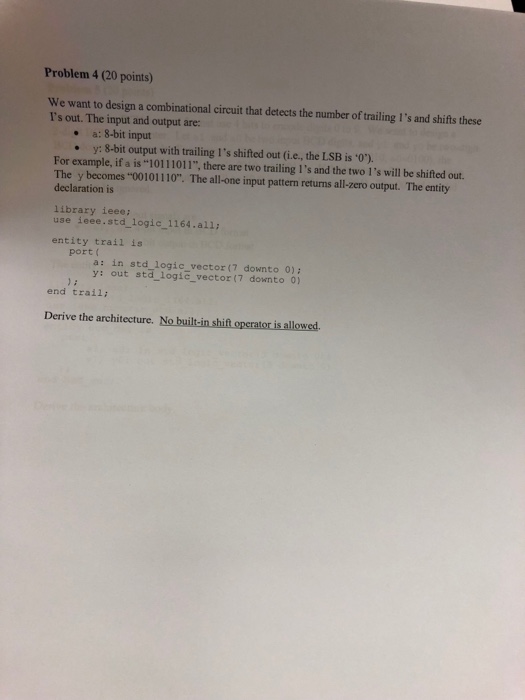

Problem 4 (20 points) We want to design a combinational circuit that detects the number of trailing I's and shifts these I's out. The input and output are: . a: 8-bit input y: 8-bit output with trailing l's shifted out (ie, the LSB is-0"). For example, if a is "10111011", there are two trailing I's and the two I's will be shifted out. The y becomes "00101110". The all-one input pattern returns all-zero output. The entity declaration is library ieee: use ieee.std logic 1164.all: entity trail is port ( a: in std _logic_vector (7 downto 0): y: out std logic_vector (7 downto 0) end trail; Derive the architecture. No built-in shift operator is allowed

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts