Question: Problem 4: New LC2K Processor (30 points) Your company has been producing a 1GHz version of the LC2K pipelined processor (as described in class, using

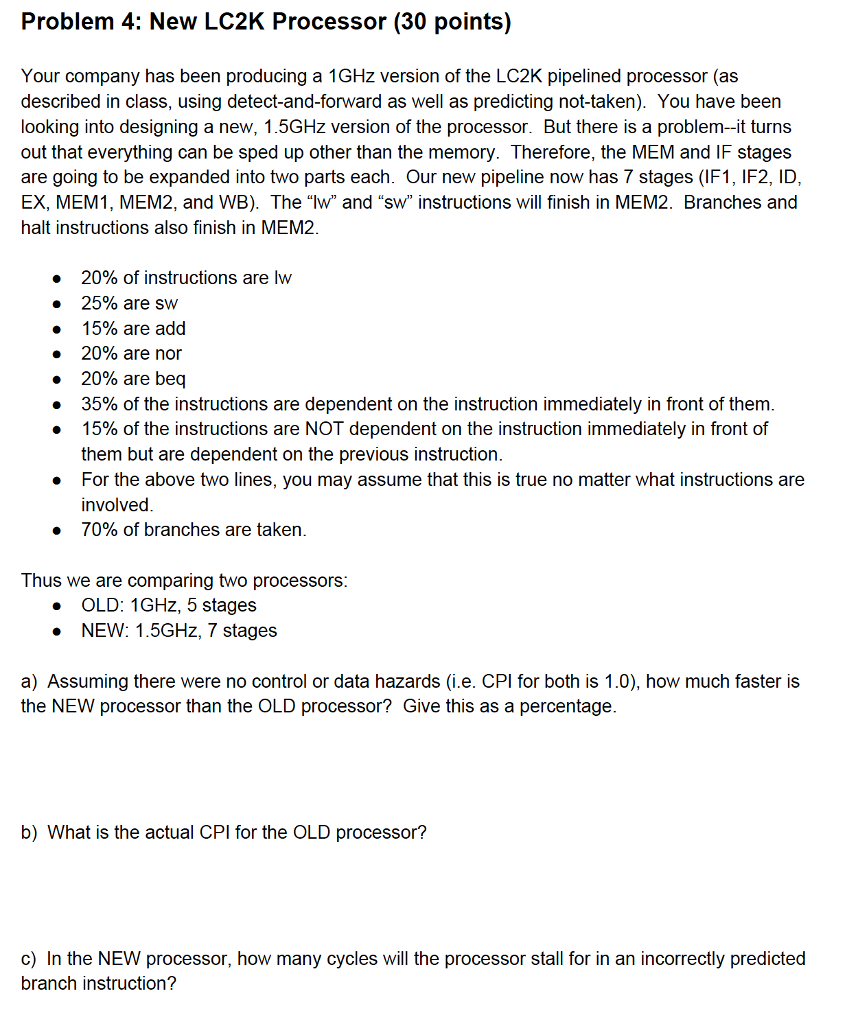

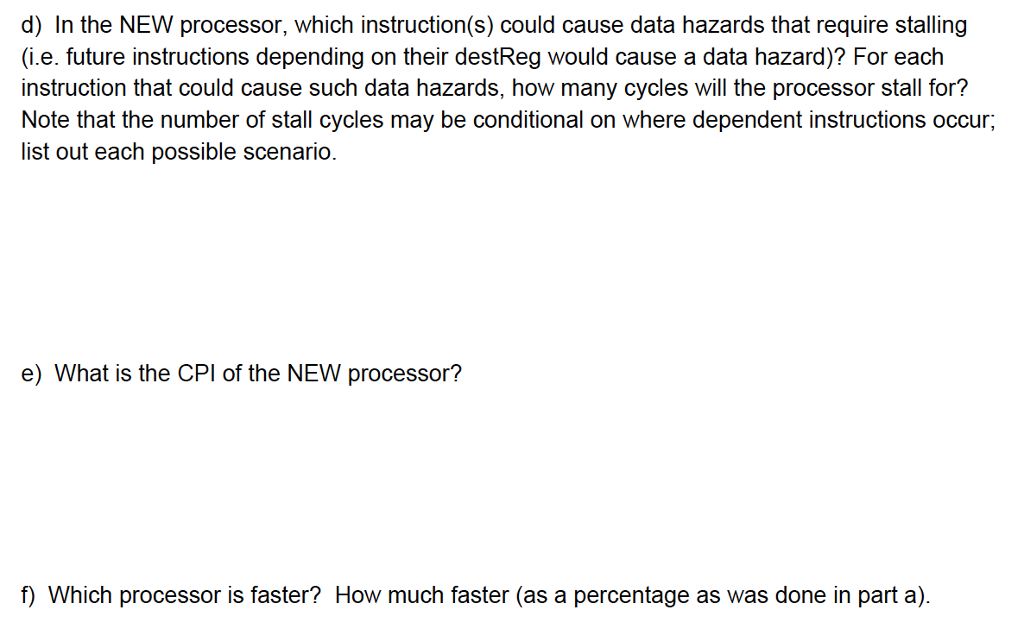

Problem 4: New LC2K Processor (30 points) Your company has been producing a 1GHz version of the LC2K pipelined processor (as described in class, using detect-and-forward as well as predicting not-taken). You have been looking into designing a new, 1.5GHz version of the processor. But there is a problem--it turns out that everything can be sped up other than the memory. Therefore, the MEM and IF stages are going to be expanded into two parts each. Our new pipeline now has 7 stages (IF1, IF2, ID, EX, MEM1, MEM2, and WB). The "w" and "sw" instructions will finish in MEM2. Branches and halt instructions also finish in MEM2 20% of instructions are lw 25% are sw 15% are add 20% are nor 20% are beq 35% of the instructions are dependent on the instruction immediately in front of them 15% of the instructions are NOT dependent on the instruction immediately in front of them but are dependent on the previous instruction For the above two lines, you may assume that this is true no matter what instructions are involved 70% of branches are taken . . Thus we are comparing two processors OLD: 1GHz, 5 stages NEW: 1.5GHz, 7 stages a) Assuming there were no control or data hazards (i.e. CPl for both is 1.0), how much faster is the NEW processor than the OLD processor? Give this as a percentage b) What is the actual CPI for the OLD processor? c) In the NEW processor, how many cycles will the processor stall for in an incorrectly predicted branch instruction? Problem 4: New LC2K Processor (30 points) Your company has been producing a 1GHz version of the LC2K pipelined processor (as described in class, using detect-and-forward as well as predicting not-taken). You have been looking into designing a new, 1.5GHz version of the processor. But there is a problem--it turns out that everything can be sped up other than the memory. Therefore, the MEM and IF stages are going to be expanded into two parts each. Our new pipeline now has 7 stages (IF1, IF2, ID, EX, MEM1, MEM2, and WB). The "w" and "sw" instructions will finish in MEM2. Branches and halt instructions also finish in MEM2 20% of instructions are lw 25% are sw 15% are add 20% are nor 20% are beq 35% of the instructions are dependent on the instruction immediately in front of them 15% of the instructions are NOT dependent on the instruction immediately in front of them but are dependent on the previous instruction For the above two lines, you may assume that this is true no matter what instructions are involved 70% of branches are taken . . Thus we are comparing two processors OLD: 1GHz, 5 stages NEW: 1.5GHz, 7 stages a) Assuming there were no control or data hazards (i.e. CPl for both is 1.0), how much faster is the NEW processor than the OLD processor? Give this as a percentage b) What is the actual CPI for the OLD processor? c) In the NEW processor, how many cycles will the processor stall for in an incorrectly predicted branch instruction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts