Question: Problem 5 Consider a homogeneous multicore machine containing two single-thread processor cores and four shared memory modules, MiM2, M, M4. The oores and memories are

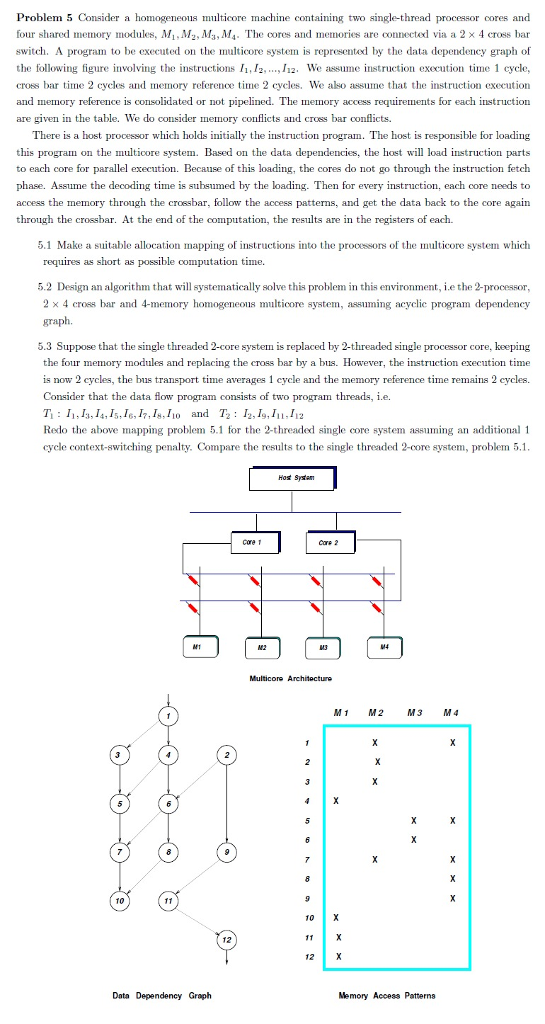

Problem 5 Consider a homogeneous multicore machine containing two single-thread processor cores and four shared memory modules, MiM2, M, M4. The oores and memories are oonnected via a 2 x 4 cross bar swch. A program to be executed on the multicore system is representod by the data dependency graph of the following figure involving the structis , I2, 112. We assume instruction execution time 1 cycle, cross bar tie2 cycles and memory reference time 2 cycles. We also assume that the instruction execution and memory reference is consolidated or not pipelined. The memory access requirements for each instruction are given in the table. We do consider memory conflicts and cross bar conflicts There is a host processor which holds initially the instruction program. The host is responsible for loading this progra on the multicore syst. Based on the data depies, the host will load instruction parts to each core for parallel execution. Because of this loading, the cores do not go through the instruction fetch phase. Assume the decoding time is suhsumed by the loading. Then for every instruction, each core needs to access the memory through the crossbar, follow the access patterns, and get the data back to the core again through the crossbar. At the end of the computation, the results are in the registers of each. 5.1 Make a suitable allocation api of instructions into the prooessors of the multicore system which requires as short as possible computation time. 5.2 Design an algorithm that will systematically solve this problem in this environment, i.e the 2-processor 2 x 4 cros bar and 4-memory homogeneous multicore system, assuming acyic program dependency 5.3 Suppose that the single threaded 2-core syste is replaced by 2-threaded single processor core, keeping the four memory modules and replacing the cross bar by a bus. However, the instruction execution time is now 2 cycles, the bus transport time averages 1 cycle and the memory reference time remains 2 cycles Consider that the data flow program T: II,14, 15,I6, 17, Is,Io and Tz: /2, I,II2 Redo the above mapping problem 5.1 for the 2-threaded single core system assuming an additional 1 cycle context-switching penalty. Compare the results to the single threaded 2-core system, problem 5.1 consists of two program threads, i.e. Core T Core 2 M1 M2 M3 M4 1o 10 X 12 12X Data Dependency Graph Memory Access Patterns Problem 5 Consider a homogeneous multicore machine containing two single-thread processor cores and four shared memory modules, MiM2, M, M4. The oores and memories are oonnected via a 2 x 4 cross bar swch. A program to be executed on the multicore system is representod by the data dependency graph of the following figure involving the structis , I2, 112. We assume instruction execution time 1 cycle, cross bar tie2 cycles and memory reference time 2 cycles. We also assume that the instruction execution and memory reference is consolidated or not pipelined. The memory access requirements for each instruction are given in the table. We do consider memory conflicts and cross bar conflicts There is a host processor which holds initially the instruction program. The host is responsible for loading this progra on the multicore syst. Based on the data depies, the host will load instruction parts to each core for parallel execution. Because of this loading, the cores do not go through the instruction fetch phase. Assume the decoding time is suhsumed by the loading. Then for every instruction, each core needs to access the memory through the crossbar, follow the access patterns, and get the data back to the core again through the crossbar. At the end of the computation, the results are in the registers of each. 5.1 Make a suitable allocation api of instructions into the prooessors of the multicore system which requires as short as possible computation time. 5.2 Design an algorithm that will systematically solve this problem in this environment, i.e the 2-processor 2 x 4 cros bar and 4-memory homogeneous multicore system, assuming acyic program dependency 5.3 Suppose that the single threaded 2-core syste is replaced by 2-threaded single processor core, keeping the four memory modules and replacing the cross bar by a bus. However, the instruction execution time is now 2 cycles, the bus transport time averages 1 cycle and the memory reference time remains 2 cycles Consider that the data flow program T: II,14, 15,I6, 17, Is,Io and Tz: /2, I,II2 Redo the above mapping problem 5.1 for the 2-threaded single core system assuming an additional 1 cycle context-switching penalty. Compare the results to the single threaded 2-core system, problem 5.1 consists of two program threads, i.e. Core T Core 2 M1 M2 M3 M4 1o 10 X 12 12X Data Dependency Graph Memory Access Patterns

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts