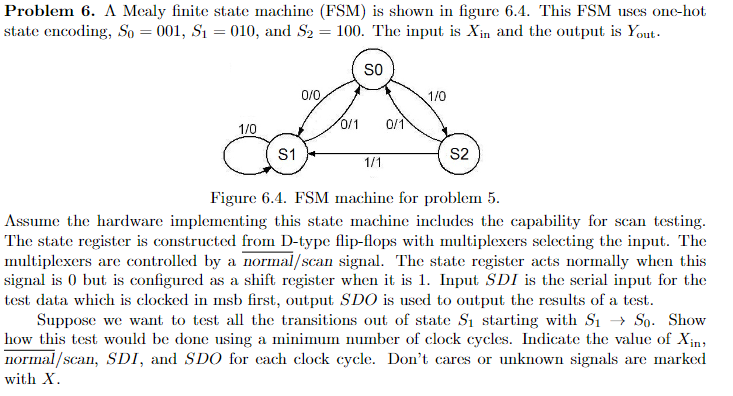

Question: Problem 6 . 1 Mealy finite state machine ( FSM ) is shown in figure 6 . 4 . This FSM uses one - hot

Problem Mealy finite state machine FSM is shown in figure This FSM uses onehot

state encoding, SS and S The input is xin and the output is Yout

Figure FSM machine for problem

Assume the hardware implementing this state machine includes the capability for scan testing.

The state register is constructed from Dtype flipflops with multiplexers selecting the input. The

multiplexers are controlled by a normalscan signal. The state register acts normally when this

signal is but is configured as a shift register when it is Input SDI is the serial input for the

test data which is clocked in msb first, output SDO is used to output the results of a test.

Suppose we want to test all the transitions out of state S starting with SS Show

how this test would be done using a minimum number of clock cycles. Indicate the value of xin

bar normal scanSDI, and SDO for each clock cycle. Don't cares or unknown signals are marked

with x

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock