Question: Problem 8 A five instruction sequence executes according to Tomasulo's algorithm. Each instruction is of the form ADD DR , SR 1 , SR 2

Problem

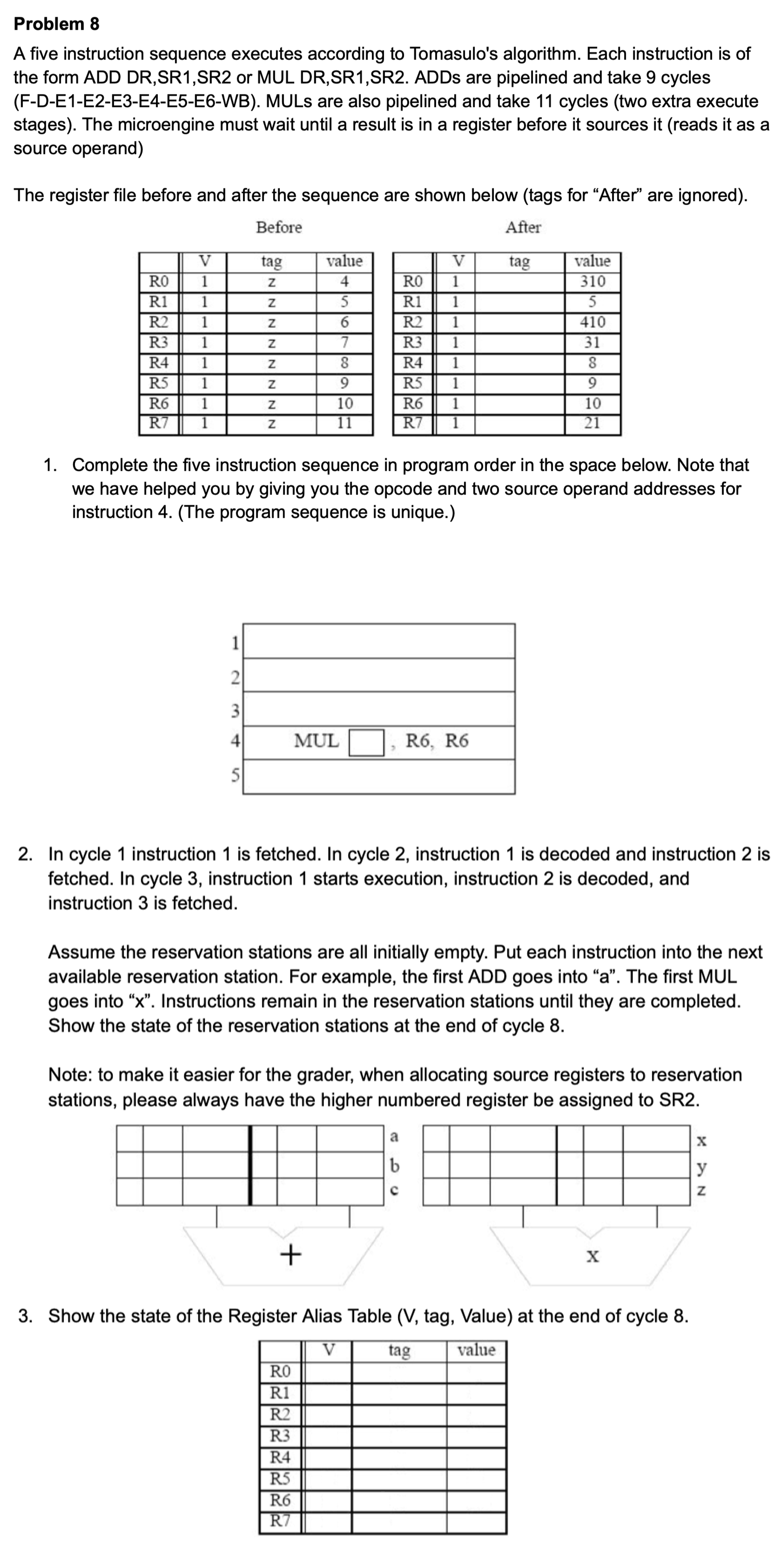

A five instruction sequence executes according to Tomasulo's algorithm. Each instruction is of the form ADD DRSRSR or MUL DRSRSR ADDs are pipelined and take cycles FDEEEEEEWB MULs are also pipelined and take cycles two extra execute stages The microengine must wait until a result is in a register before it sources it reads it as a source operand

The register file before and after the sequence are shown below tags for "After" are ignored

Before

After

tableVtag,valueRzRzRzRzRzRzRzRz

tableVtag,valueRRRRRRRR

Complete the five instruction sequence in program order in the space below. Note that we have helped you by giving you the opcode and two source operand addresses for instruction The program sequence is unique.

tableMUL,, R R

In cycle instruction is fetched. In cycle instruction is decoded and instruction is fetched. In cycle instruction starts execution, instruction is decoded, and instruction is fetched.

Assume the reservation stations are all initially empty. Put each instruction into the next available reservation station. For example, the first ADD goes into The first MUL goes into Instructions remain in the reservation stations until they are completed. Show the state of the reservation stations at the end of cycle

Note: to make it easier for the grader, when allocating source registers to reservation statinno ninace olusove houn tha hinhar numbarad manictar ha acoinnod tn CD

Show the state of the Register Alias Table V tag, Value at the end of cycle

tableVtag,valueRRRRRRRR

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock