Question: Q 1 ) 3 0 points ( 5 + 1 5 + 1 0 ) The following circuits shows 4 - bit Synchronous Counter with

Q points

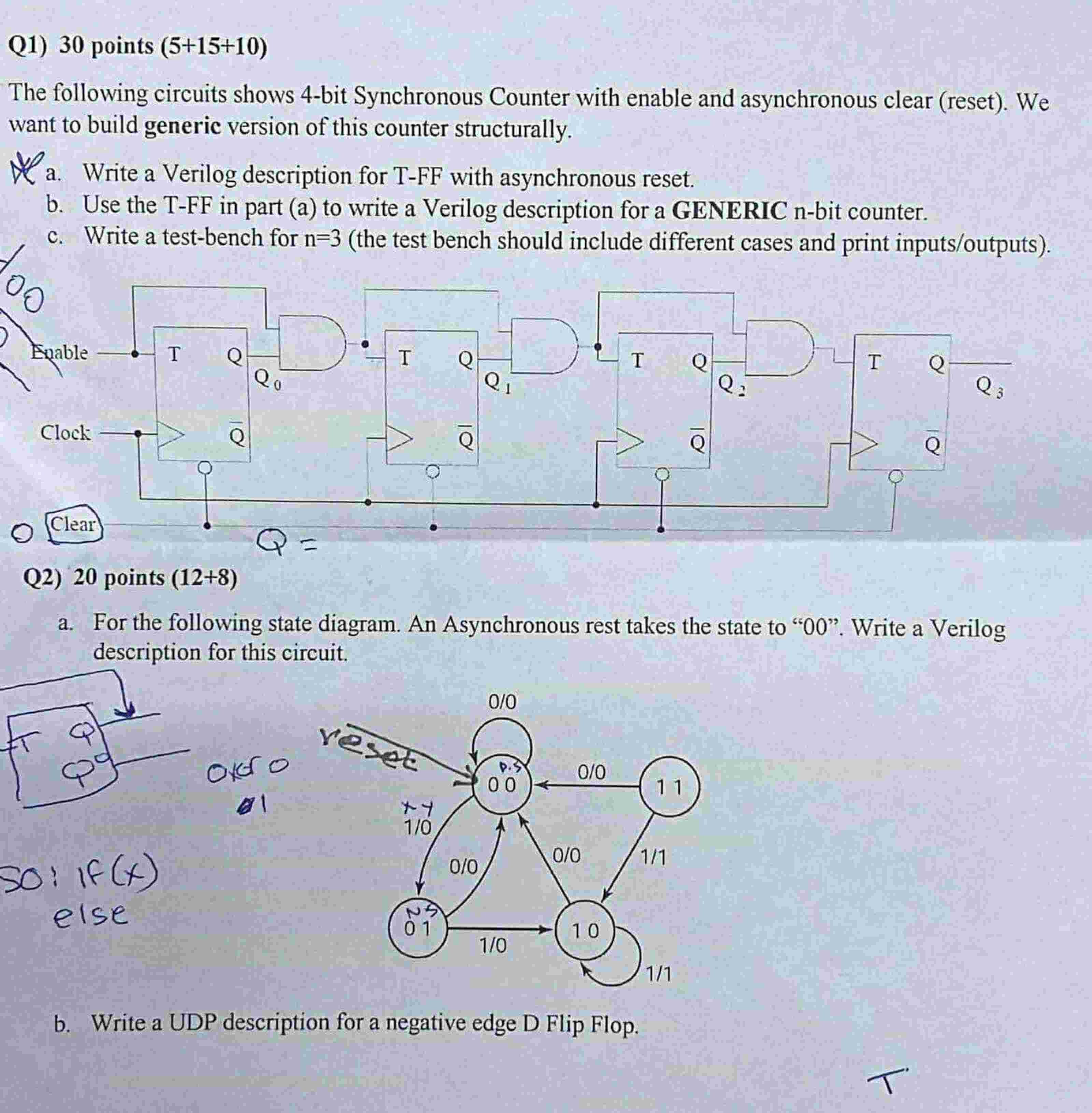

The following circuits shows bit Synchronous Counter with enable and asynchronous clear reset We want to build generic version of this counter structurally.

a Write a Verilog description for TFF with asynchronous reset.

b Use the TFF in part a to write a Verilog description for a GENERIC nbit counter.

c Write a testbench for nthe test bench should include different cases and print inputsoutputs

a For the following state diagram. An Asynchronous rest takes the state to Write a Verilog description for this circuit.

b Write a UDP description for a negative edge D Flip Flop. Q points

The following circuits shows bit Synchronous Counter with enable and asynchronous clear reset We want to build generic version of this counter structurally.

a Write a Verilog description for TFF with asynchronous reset.

b Use the TFF in part a to write a Verilog description for a GENERIC nbit counter.

c Write a testbench for mathrmnthe test bench should include different cases and print inputsoutputs

Q points mathbf

a For the following state diagram. An Asynchronous rest takes the state to Write a Verilog description for this circuit.

b Write a UDP description for a negative edge D Flip Flop.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock