Question: Q 1 : Design a Half Adder using NAND Gates only: Step 1 : Understanding the Half Adder Function: Carry = AB Sum = (

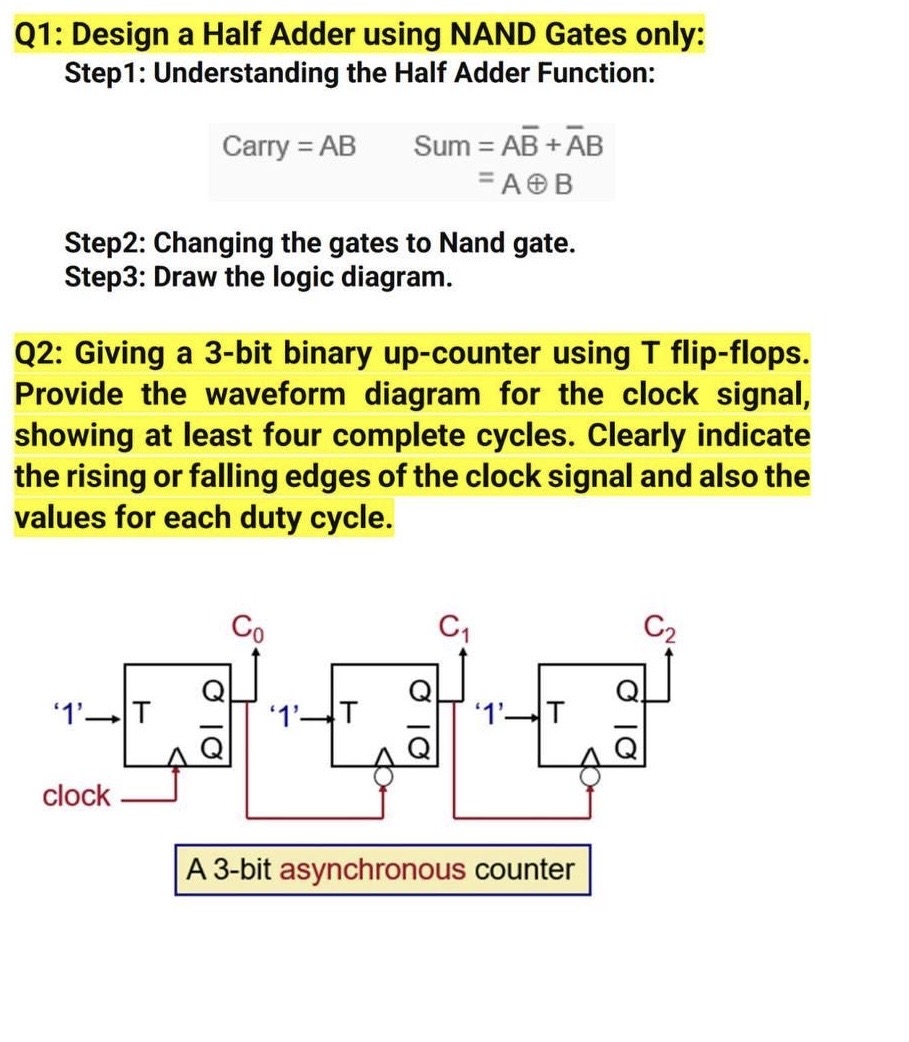

Q: Design a Half Adder using NAND Gates only:

Step: Understanding the Half Adder Function:

Carry AB Sum Abar Bbar AB

AoB

Step: Changing the gates to Nand gate.

Step: Draw the logic diagram.

Q: Giving a bit binary upcounter using T flipflops.

Provide the waveform diagram for the clock signal,

showing at least four complete cycles. Clearly indicate

the rising or falling edges of the clock signal and also the

values for each duty cycle.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock