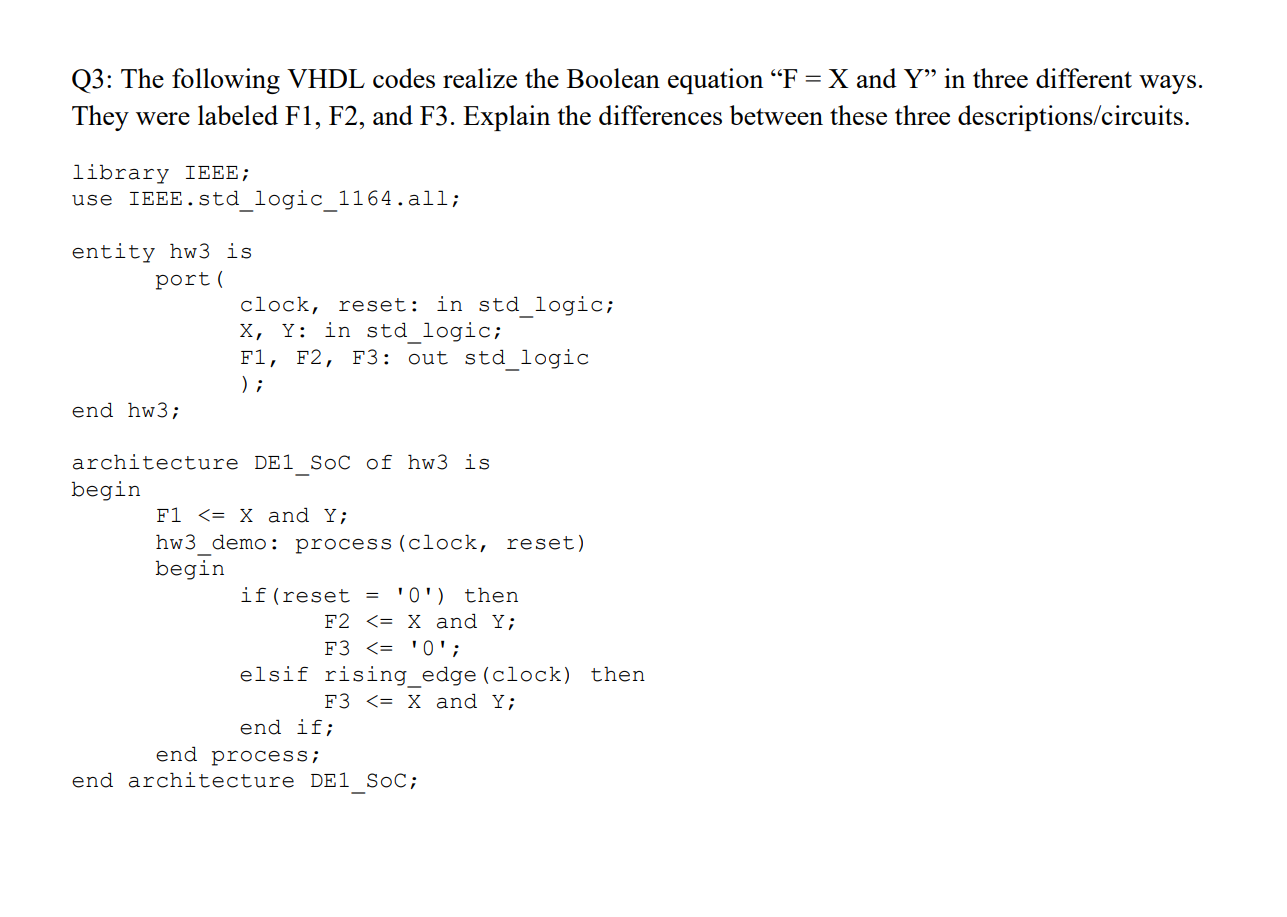

Question: Q 3 : The following VHDL codes realize the Boolean equation F = x and Y in three different ways. They were labeled

Q: The following VHDL codes realize the Boolean equation and in three different ways.

They were labeled F F and F Explain the differences between these three descriptionscircuits

library IEEE;

use IEEE.stdlogicall;

entity hw is

port

clock, reset: in stdlogic;

: in stdlogic;

F F F: out stdlogic

;

end hw;

architecture DESoC of hw is

begin

and ;

hwdemo: process clock reset

begin

if reset then

and ;

F;

elsif risingedgeclock then

and ;

end if;

end process;

end architecture DESoC;

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock