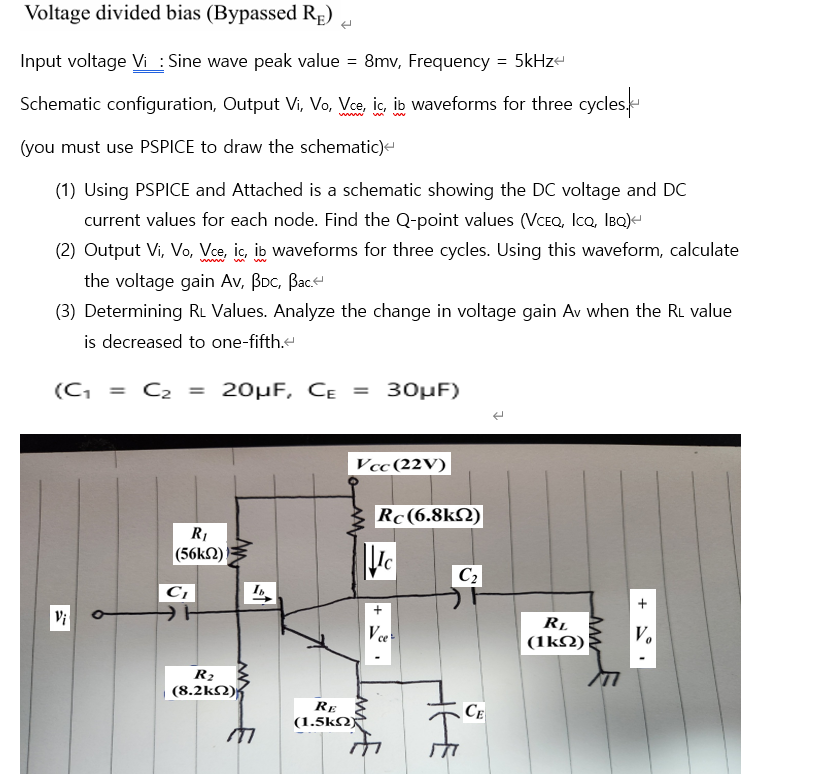

Question: Q . Voltage divided bias ( Bypassed R E ) Schematic configuration, Output V i , V o , V c e , ic ,

Q Voltage divided bias Bypassed

Schematic configuration, Output ic ic ib waveforms for three cycles.

you must use Orcad PSPICE to draw the schematic

Using Orcad PSPICE shcematics and Attached is a schematic showing the DC voltage and DC current values for each node. Find the Qpoint values

Output ib waveforms for three cycles. Using this waveform, calculate the voltage gain

Determining RL Values. Analyze the change in voltage gain when the RL value is decreased to onefifth.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock