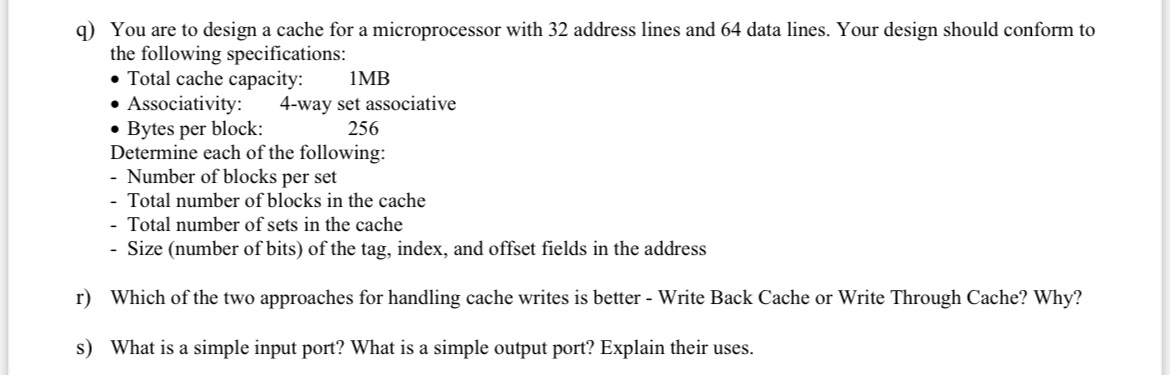

Question: q ) You are to design a cache for a microprocessor with 3 2 address lines and 6 4 data lines. Your design should conform

q You are to design a cache for a microprocessor with address lines and data lines. Your design should conform to the following specifications:

Total cache capacity:

Associativity: way set associative

Bytes per block:

Determine each of the following:

Number of blocks per set

Total number of blocks in the cache

Total number of sets in the cache

Size number of bits of the tag, index, and offset fields in the address

r Which of the two approaches for handling cache writes is better Write Back Cache or Write Through Cache? Why?

s What is a simple input port? What is a simple output port? Explain their uses.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock