Question: (Q1) Develop and verify (create a testbench, too ) a Verilog module that produces a 4-bit output code indicating the number of l's in an

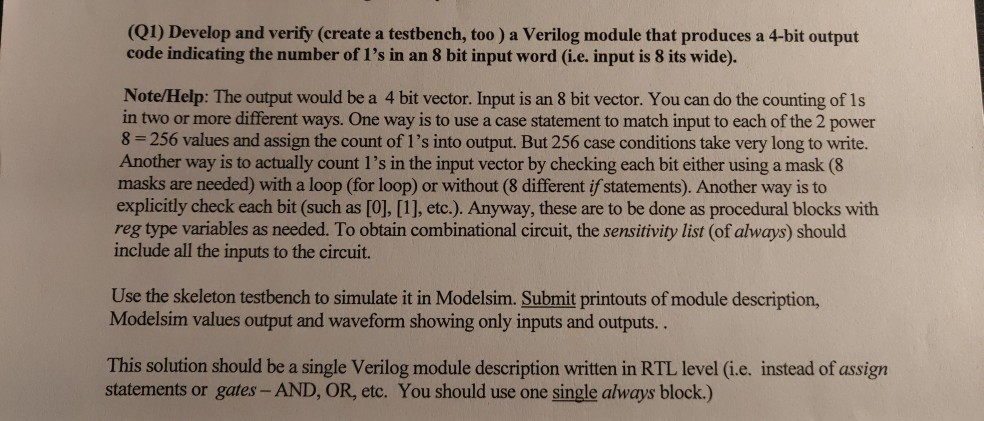

(Q1) Develop and verify (create a testbench, too ) a Verilog module that produces a 4-bit output code indicating the number of l's in an 8 bit input word (i.e. input is 8 its wide). Note/Help: The output would be a 4 bit vector. Input is an 8 bit vector. You can do the counting of 1s in two or more different ways. One way is to use a case statement to match input to each of the 2 power 8 = 256 values and assign the count of 1's into output. But 256 case conditions take very long to write. Another way is to actually count l's in the input vector by checking each bit either using a mask (8 masks are needed) with a loop (for loop) or without (8 different if statements). Another way is to explicitly check each bit (such as [0], [1], etc.). Anyway, these are to be done as procedural blocks with reg type variables as needed. To obtain combinational circuit, the sensitivity list (of always) should include all the inputs to the circuit. Use the skeleton testbench to simulate it in Modelsim. Submit printouts of module description, Modelsim values output and waveform showing only inputs and outputs.. This solution should be a single Verilog module description written in RTL level (i.e. instead of assign statements or gates - AND, OR, etc. You should use one single always block.)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts