Question: Q6- Consider a Tomasulo's algorithm in the execution of the code below with the following latencies: add is 2 clock cycles, and multiply is 6

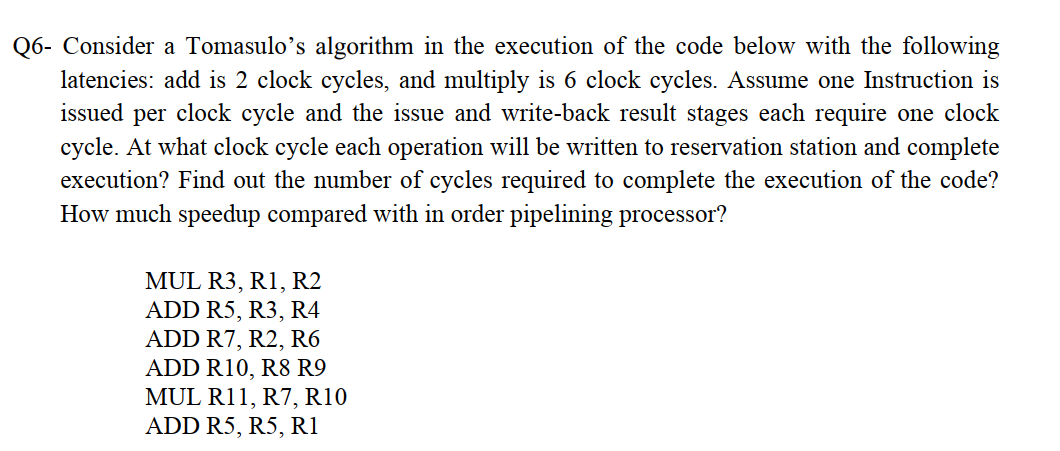

Q6- Consider a Tomasulo's algorithm in the execution of the code below with the following latencies: add is 2 clock cycles, and multiply is 6 clock cycles. Assume one Instruction is issued per clock cycle and the issue and write-back result stages each require one clock cycle. At what clock cycle each operation will be written to reservation station and complete execution? Find out the number of cycles required to complete the execution of the code? How much speedup compared with in order pipelining processor? MUL R3, R1, R2 ADD R5, R3, R4 ADD R7, R2, R6 ADD R10, R8 R9 MUL R11, R7, R10 ADD R5, R5, R1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts