Question: Question 1 (10 points) Design and implement a 2-bit synchronous counter using at least 1 T-Flip Flop and 1 JK-Flip Flop. This 2-bit counter has

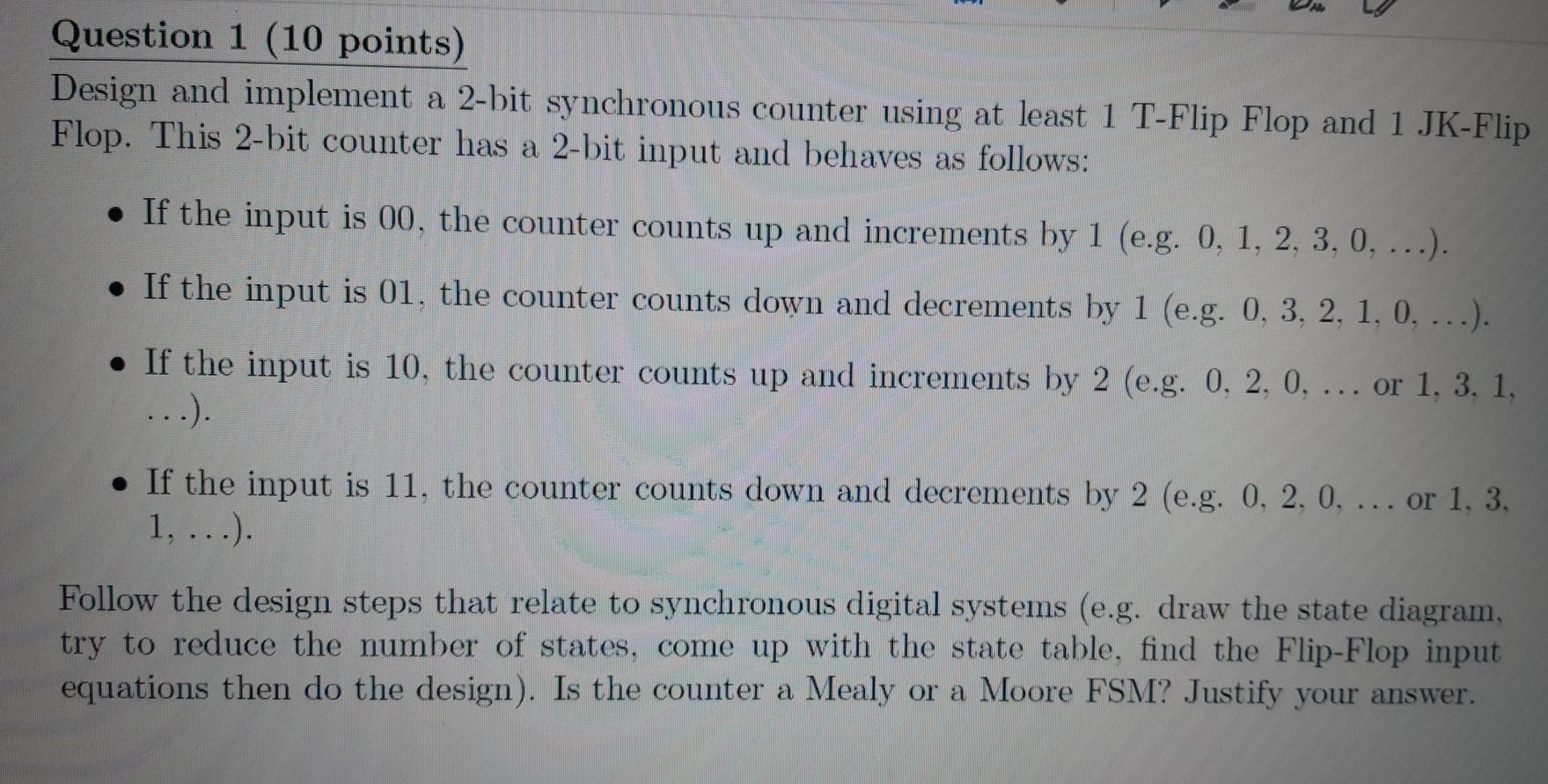

Question 1 (10 points) Design and implement a 2-bit synchronous counter using at least 1 T-Flip Flop and 1 JK-Flip Flop. This 2-bit counter has a 2-bit input and behaves as follows: If the input is 00, the counter counts up and increments by 1 (e.g. 0, 1, 2, 3, 0, ...). If the input is 01, the counter counts down and decrements by 1 (e.g. 0, 3, 2, 1, 0, ...). If the input is 10, the counter counts up and increments by 2 (e.g. 0, 2, 0, ... or 1, 3.1, If the input is 11, the counter counts down and decrements by 2 (e.g. 0, 2, 0, ... or 1, 3, 1, ...). Follow the design steps that relate to synchronous digital systems (e.g. draw the state diagram, try to reduce the number of states, come up with the state table, find the Flip-Flop input equations then do the design). Is the counter a Mealy or a Moore FSM? Justify your

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts