Question: Question 1 Pipelining (15 points) We have a machine with the following pipeline: IF 1 TLB lookup of instruction address IF2 Instruction cache access ID

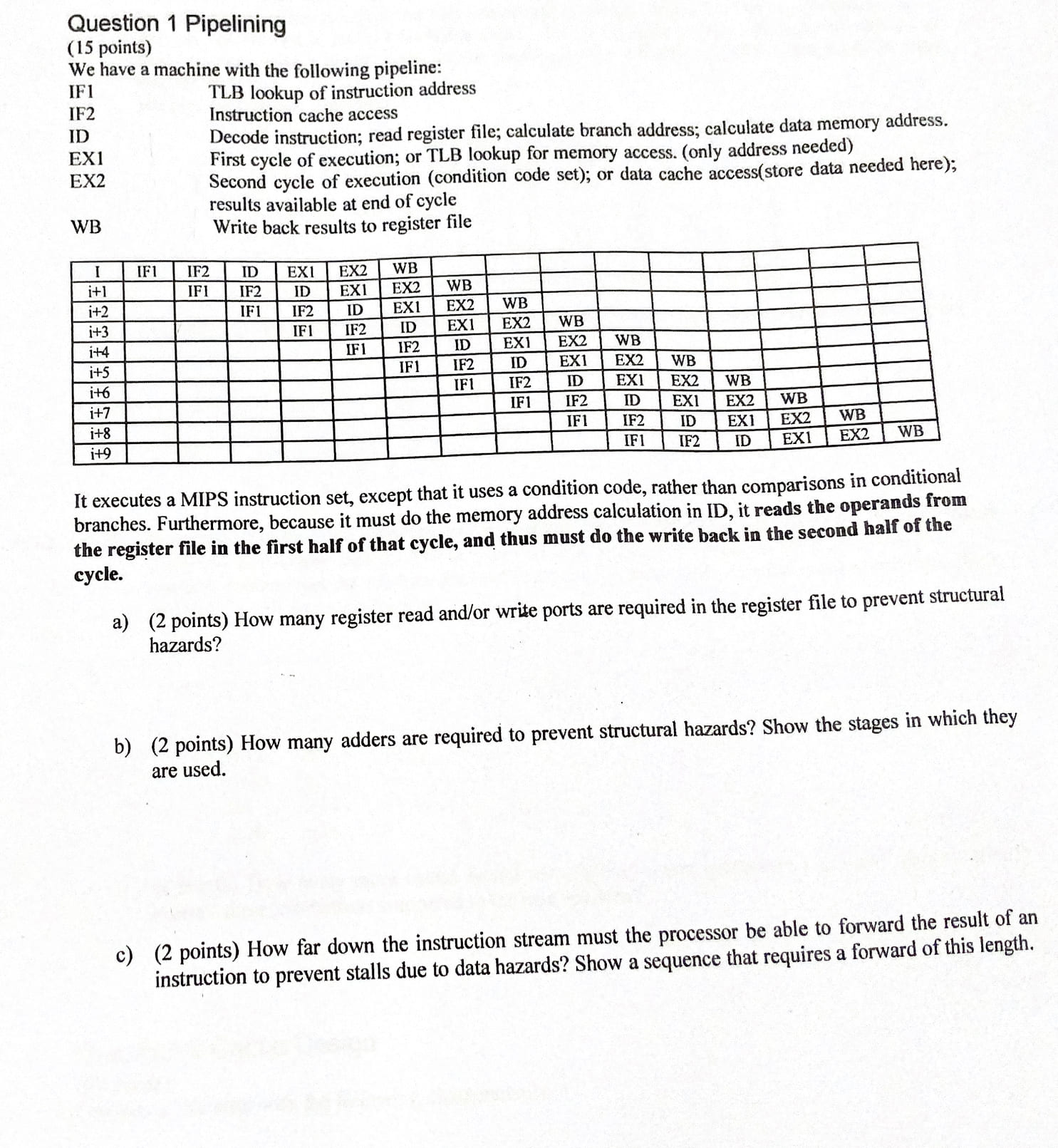

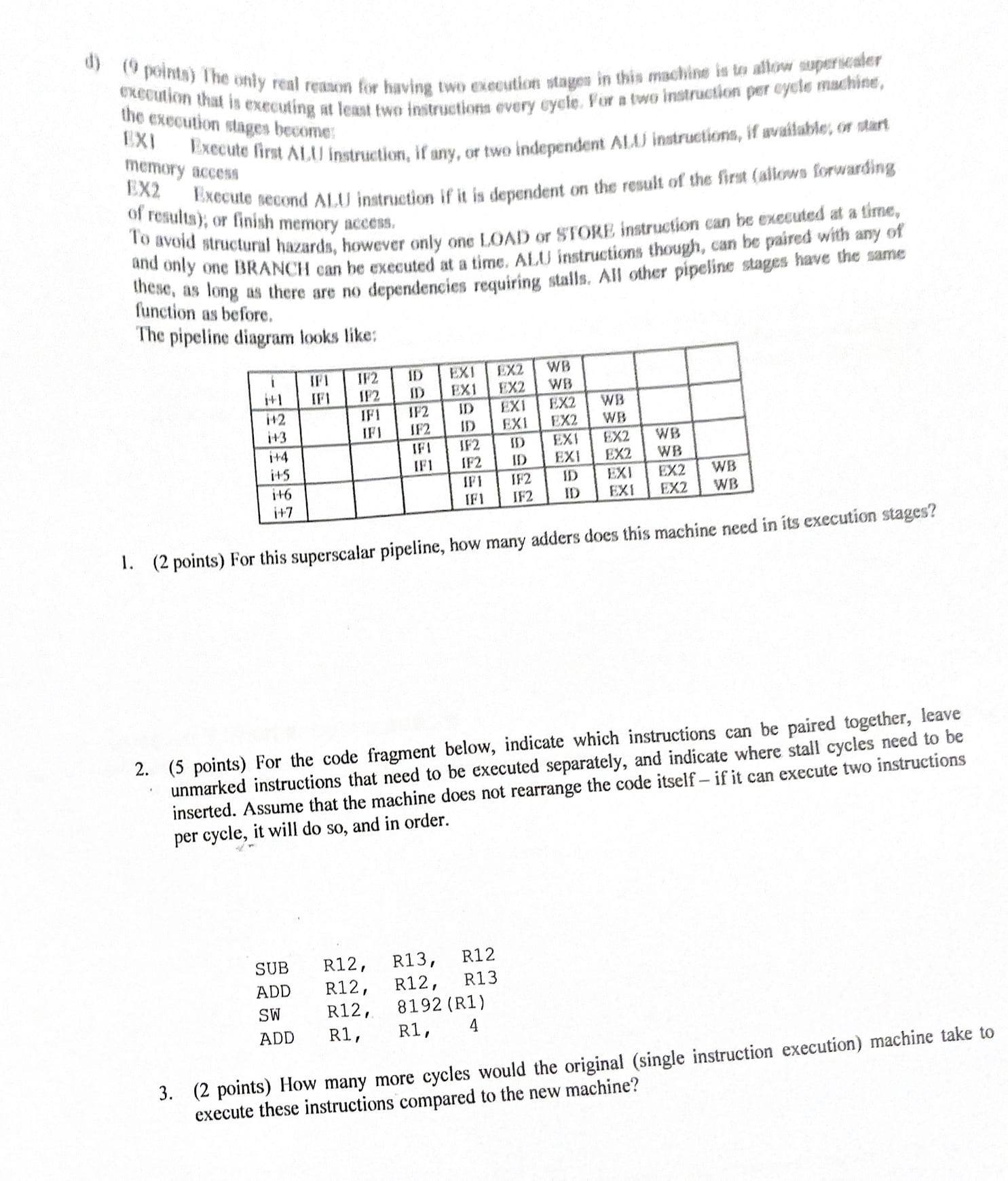

Question 1 Pipelining (15 points) We have a machine with the following pipeline: IF 1 TLB lookup of instruction address IF2 Instruction cache access ID Decode instruction; read register file; calculate branch address; calculate data memory address. EX1 First cycle of execution; or TLB lookup for memory access. (only address needed) EX2 Second cycle of execution (condition code set); or data cache access(store data needed here); results available at end of cycle WB Write back results to register file It executes a MIPS instruction set, except that it uses a condition code, rather than comparisons in conditional branches. Furthermore, because it must do the memory address calculation in ID, it reads the operands from the register file in the first half of that cycle, and thus must do the write back in the second half of the cycle. a) (2 points) How many register read and/or write ports are required in the register file to prevent structural hazards? b) (2 points) How many adders are required to prevent structural hazards? Show the stages in which they are used. c) (2 points) How far down the instruction stream must the processor be able to forward the result of an instruction to prevent stalls due to data hazards? Show a sequence that requires a forward of this length. d) (9 pointa) The onily real reaun for having two execution stagen in tha machine is tu allow supericaler execution that is executing at least two instructions every eycle. For a two instruction per eycls machise, the execution stages become: IXI Erecute first ALU instructioni, if any, of two independent ALU instructions, if watable, of anant memory accest EX2 Execute second ALU instruction if it is dependent on the result of the first (allows forwarding of results), or finish memory access. To avoid structural hazards, however only one LOAD or STORE instruction can be exeeuted at a time, and only one BRANCH can be executed at a time. ALU instructions though, can be paired with any of these, as long as there are no dependencies requiring stalls. All other pipeline stages have the same function as before. The pipeline diagram looks like: 1. (2 points) For this superscalar pipeline, how many adders does this machine necu in its execution stages? 2. (5 points) For the code fragment below, indicate which instructions can be paired together, leave unmarked instructions that need to be executed separately, and indicate where stall cycles need to be inserted. Assume that the machine does not rearrange the code itself - if it can execute two instructions per cycle, it will do so, and in order. 3. (2 points) How many more cycles would the original (single instruction execution) machine take to execute these instructions compared to the new machine? Question 1 Pipelining (15 points) We have a machine with the following pipeline: IF 1 TLB lookup of instruction address IF2 Instruction cache access ID Decode instruction; read register file; calculate branch address; calculate data memory address. EX1 First cycle of execution; or TLB lookup for memory access. (only address needed) EX2 Second cycle of execution (condition code set); or data cache access(store data needed here); results available at end of cycle WB Write back results to register file It executes a MIPS instruction set, except that it uses a condition code, rather than comparisons in conditional branches. Furthermore, because it must do the memory address calculation in ID, it reads the operands from the register file in the first half of that cycle, and thus must do the write back in the second half of the cycle. a) (2 points) How many register read and/or write ports are required in the register file to prevent structural hazards? b) (2 points) How many adders are required to prevent structural hazards? Show the stages in which they are used. c) (2 points) How far down the instruction stream must the processor be able to forward the result of an instruction to prevent stalls due to data hazards? Show a sequence that requires a forward of this length. d) (9 pointa) The onily real reaun for having two execution stagen in tha machine is tu allow supericaler execution that is executing at least two instructions every eycle. For a two instruction per eycls machise, the execution stages become: IXI Erecute first ALU instructioni, if any, of two independent ALU instructions, if watable, of anant memory accest EX2 Execute second ALU instruction if it is dependent on the result of the first (allows forwarding of results), or finish memory access. To avoid structural hazards, however only one LOAD or STORE instruction can be exeeuted at a time, and only one BRANCH can be executed at a time. ALU instructions though, can be paired with any of these, as long as there are no dependencies requiring stalls. All other pipeline stages have the same function as before. The pipeline diagram looks like: 1. (2 points) For this superscalar pipeline, how many adders does this machine necu in its execution stages? 2. (5 points) For the code fragment below, indicate which instructions can be paired together, leave unmarked instructions that need to be executed separately, and indicate where stall cycles need to be inserted. Assume that the machine does not rearrange the code itself - if it can execute two instructions per cycle, it will do so, and in order. 3. (2 points) How many more cycles would the original (single instruction execution) machine take to execute these instructions compared to the new machine

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts