Question: Question 2. (8 points) Q C.4 from the H&P textbook. A reduced hardware implementation of the classic five-stage RISC pipeline might use the EX stage

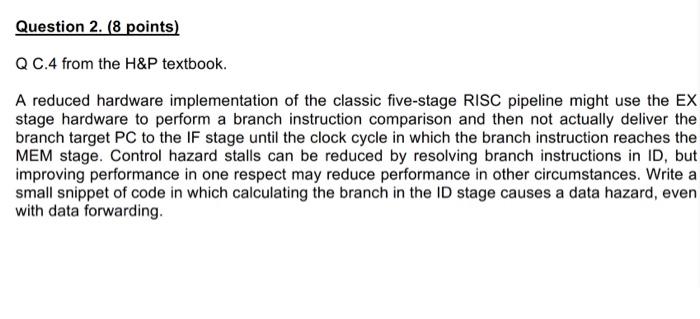

Question 2. (8 points) Q C.4 from the H&P textbook. A reduced hardware implementation of the classic five-stage RISC pipeline might use the EX stage hardware to perform a branch instruction comparison and then not actually deliver the branch target PC to the IF stage until the clock cycle in which the branch instruction reaches the MEM stage. Control hazard stalls can be reduced by resolving branch instructions in ID, but improving performance in one respect may reduce performance in other circumstances. Write a small snippet of code in which calculating the branch in the ID stage causes a data hazard, even with data forwarding

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts