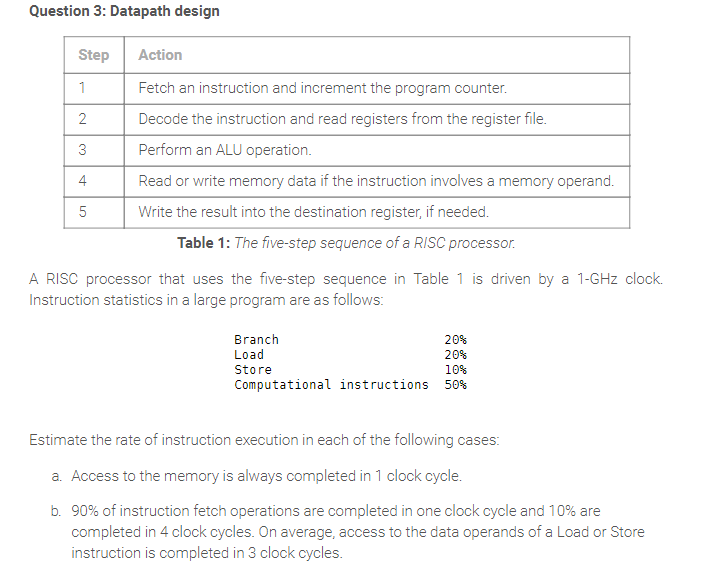

Question: Question 3: Datapath design Step Action Fetch an instruction and increment the program counter Decode the instruction and read registers from the register file. Perfo

Question 3: Datapath design Step Action Fetch an instruction and increment the program counter Decode the instruction and read registers from the register file. Perfo Al J oration. Read or write memory data if the instruction involves a memory operand. Write the result into the destination register, if needed 4 Table 1: The five-step sequence of a RISC processor A RISC processor that uses the five-step sequence in Table 1 is driven by a 1-GHz clock. Instruction statistics in a large program are as follows Branch Load Store Computational instructions 50% 20% 20% 10% Estimate the rate of instruction execution in each of the following cases: a. Access to the memory is always completed in 1 clock cycle 90% of instruction fetch operations are completed in one clock cycle and 10% are completed in 4 clock cycles. On average, access to the data operands of a Load or Store instruction is completed in 3 clock cycles b

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts