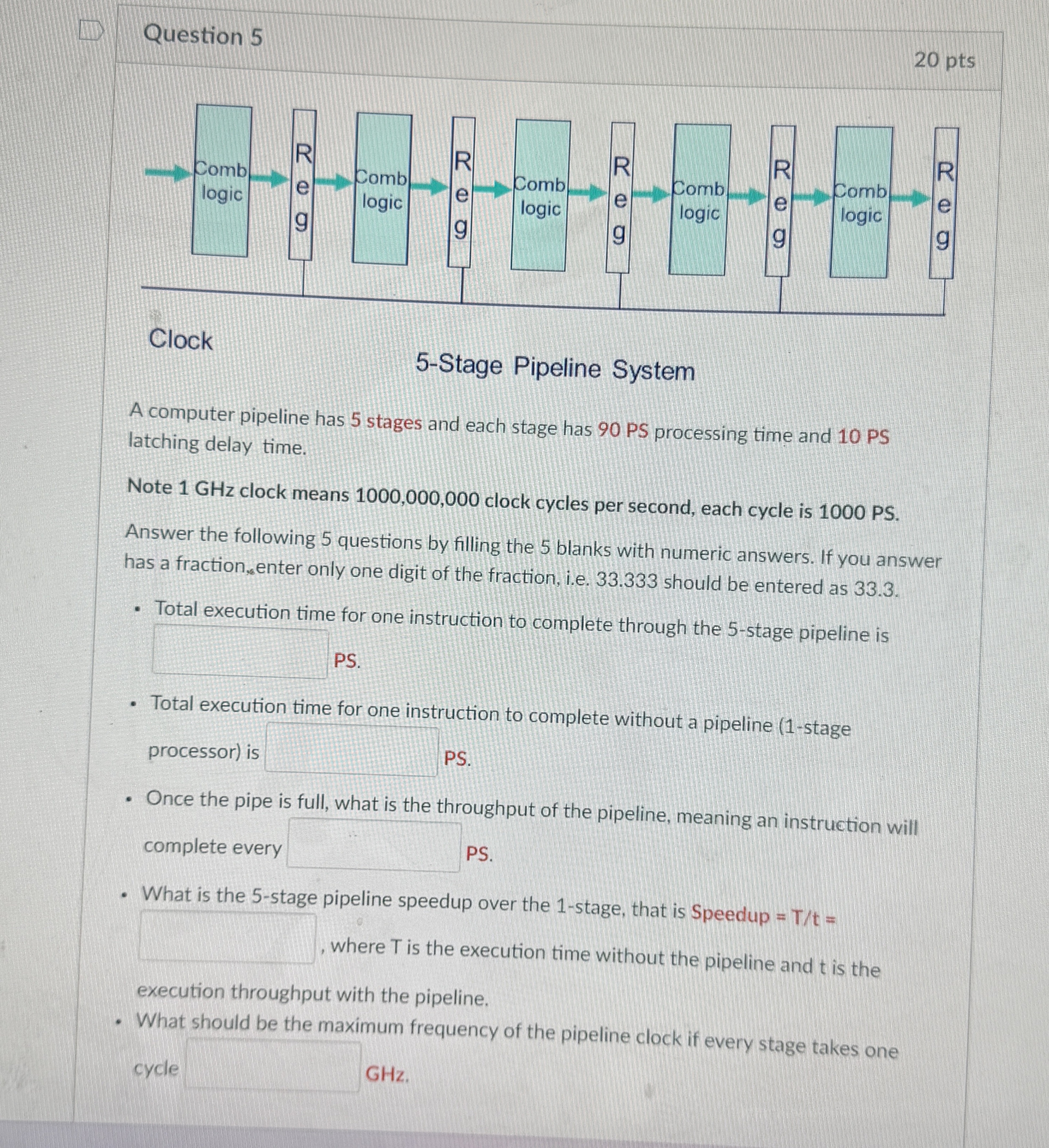

Question: Question 5 2 0 pts Clock 5 - Stage Pipeline System A computer pipeline has 5 stages and each stage has 9 0 PS processing

Question

pts

Clock

Stage Pipeline System

A computer pipeline has stages and each stage has PS processing time and PS latching delay time.

Note clock means clock cycles per second, each cycle is PS

Answer the following questions by filling the blanks with numeric answers. If you answer has a fraction.enter only one digit of the fraction, ie should be entered as

Total execution time for one instruction to complete through the stage pipeline is PS

Total execution time for one instruction to complete without a pipeline stage processor is PS

Once the pipe is full, what is the throughput of the pipeline, meaning an instruction will complete every PS

What is the stage pipeline speedup over the stage, that is Speedup where is the execution time without the pipeline and is the execution throughput with the pipeline.

What should be the maximum frequency of the pipeline clock if every stage takes one cycle

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock