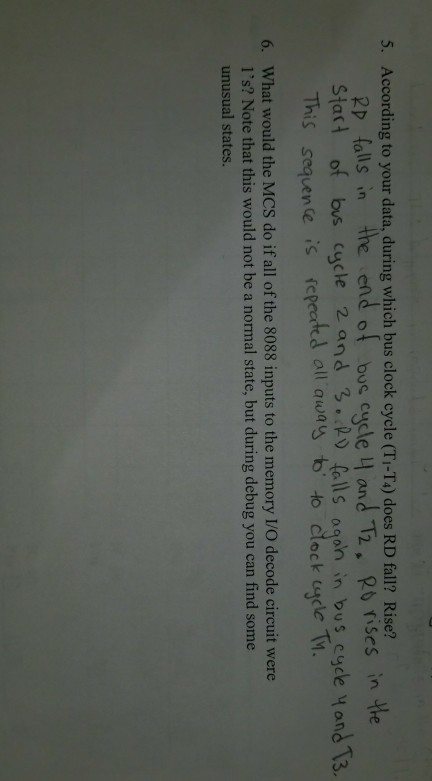

Question: Question 6. 5. According to your data, during which bus clock cycle (Ti-T4) does RD fall? Rise? RD, falls in the end of bus cycle

Question 6.

5. According to your data, during which bus clock cycle (Ti-T4) does RD fall? Rise? RD, falls in the end of bus cycle and T2. po rises in Stact of bus cycle 2and 3.P falls ogan in bus cyce yand 13 This sequence is repede to to clock uqcle Ty What would the MCS do if all of the 8088 inputs to the memory I/O decode circuit were 1's? Note that this would not be a normal state, but during debug you can find some unusual states. 6. 5. According to your data, during which bus clock cycle (Ti-T4) does RD fall? Rise? RD, falls in the end of bus cycle and T2. po rises in Stact of bus cycle 2and 3.P falls ogan in bus cyce yand 13 This sequence is repede to to clock uqcle Ty What would the MCS do if all of the 8088 inputs to the memory I/O decode circuit were 1's? Note that this would not be a normal state, but during debug you can find some unusual states. 6

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts