Question: Question 9.31 Please! floating converting a given decimal floating-point number into binary may use both the integer and floating-point instructions available in the comtormat y

Question 9.31 Please!

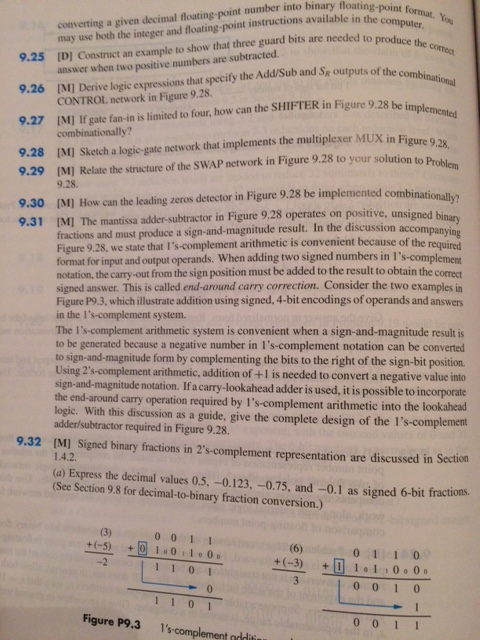

floating converting a given decimal floating-point number into binary may use both the integer and floating-point instructions available in the comtormat y computer produce the 1 Construct an example to show that three guard bits are needed to p answer when two positive numbers are subtracted comtegt 9.25 [D 26 [M] Derive logic expressions that specify the Add/Sub and Se out 9.27 [M] If gate fan-in is limited to four, how can the SHIFTER in Figure 9 9.28 [MI Sketch a logie-gate network that implements the multiplexer MUX in Fi 9. CONTROL network in Figure 9.28. combinationally igure 9.28, [MI Relate the structure of the SWAP network in Figure 9.28 to your solutio 9.28. to Problem 9.29 IM] How can the leading zeros detector in Figure 9,28 be implemented combinati [M] The mantissa adder-subtractor in Figure 9.28 operates on positive, unsi fractions and must produce a sign-and-magnitude result. In the discussion Figure 9.28, we state that I 's-complement arithmetic is convenient because of the required format for input and output operands. When adding two signed numbers in I's-complement notation, the carry-out from the sign position must be added to the result to obtain the correct signed answer. This is called end-around carry correction. Consider the two examples in 9.30 9.31 Figure P9.3, which illustrate addition using signed, 4-bit encodings of operands and answers in the I's-complement system. The I's-complement arithmetic system is convenient when a sign-and-magnitude result is to be generated because a negative number in I's-complement notation can be converted to sign-and-magnitude form by complementing the bits to the right of the sign-bit position. lement arithmetic, addition of +1 is needed to convert a negative value into nd-magnitude notation. Ifa carry-lookahead adder is used, it is possible to incorporate the end-around carry operation required by I's-complement arithmetic into the loo logic. With this discussion as a guide, give the complete design of the lI's-complement adder/subtractor required in Figure 9.28. [M] Signed binary fractions in 2's-complement representation are discussed in Section 1.4.2. (a) Express the decimal values 0.5,-0.123,-0.75. and-0.1 as signed 6-bit fractions. See Section 9.8 for decimal-to-binary fraction conversion.) 9.32 + (-5) -2 +10011000 +(-3) 10.0 0. 0 0 1 0 Figure P9.3 1's complement addit floating converting a given decimal floating-point number into binary may use both the integer and floating-point instructions available in the comtormat y computer produce the 1 Construct an example to show that three guard bits are needed to p answer when two positive numbers are subtracted comtegt 9.25 [D 26 [M] Derive logic expressions that specify the Add/Sub and Se out 9.27 [M] If gate fan-in is limited to four, how can the SHIFTER in Figure 9 9.28 [MI Sketch a logie-gate network that implements the multiplexer MUX in Fi 9. CONTROL network in Figure 9.28. combinationally igure 9.28, [MI Relate the structure of the SWAP network in Figure 9.28 to your solutio 9.28. to Problem 9.29 IM] How can the leading zeros detector in Figure 9,28 be implemented combinati [M] The mantissa adder-subtractor in Figure 9.28 operates on positive, unsi fractions and must produce a sign-and-magnitude result. In the discussion Figure 9.28, we state that I 's-complement arithmetic is convenient because of the required format for input and output operands. When adding two signed numbers in I's-complement notation, the carry-out from the sign position must be added to the result to obtain the correct signed answer. This is called end-around carry correction. Consider the two examples in 9.30 9.31 Figure P9.3, which illustrate addition using signed, 4-bit encodings of operands and answers in the I's-complement system. The I's-complement arithmetic system is convenient when a sign-and-magnitude result is to be generated because a negative number in I's-complement notation can be converted to sign-and-magnitude form by complementing the bits to the right of the sign-bit position. lement arithmetic, addition of +1 is needed to convert a negative value into nd-magnitude notation. Ifa carry-lookahead adder is used, it is possible to incorporate the end-around carry operation required by I's-complement arithmetic into the loo logic. With this discussion as a guide, give the complete design of the lI's-complement adder/subtractor required in Figure 9.28. [M] Signed binary fractions in 2's-complement representation are discussed in Section 1.4.2. (a) Express the decimal values 0.5,-0.123,-0.75. and-0.1 as signed 6-bit fractions. See Section 9.8 for decimal-to-binary fraction conversion.) 9.32 + (-5) -2 +10011000 +(-3) 10.0 0. 0 0 1 0 Figure P9.3 1's complement addit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts