Question: question: Appendix B shows a single cycle datapath implementation of MIPS. List all the instructions (from appendix A) that are not supported by the provided

question: Appendix B shows a single cycle datapath implementation of MIPS. List all the instructions (from appendix A) that are not supported by the provided datapath.

Appendix A: MIPS instruction set architecture

Instructions

o Arithmetic: add, addi, sub, mul

o Load/Store: lw, lh, lhu, lb, lbu, sw, sh, sb, lui

o Logic: sll, srl, and, andi, or, ori, nor

o Control flow: beq, bne, j, jal, jr

o Comparison: slt, slti, sltu, sltui

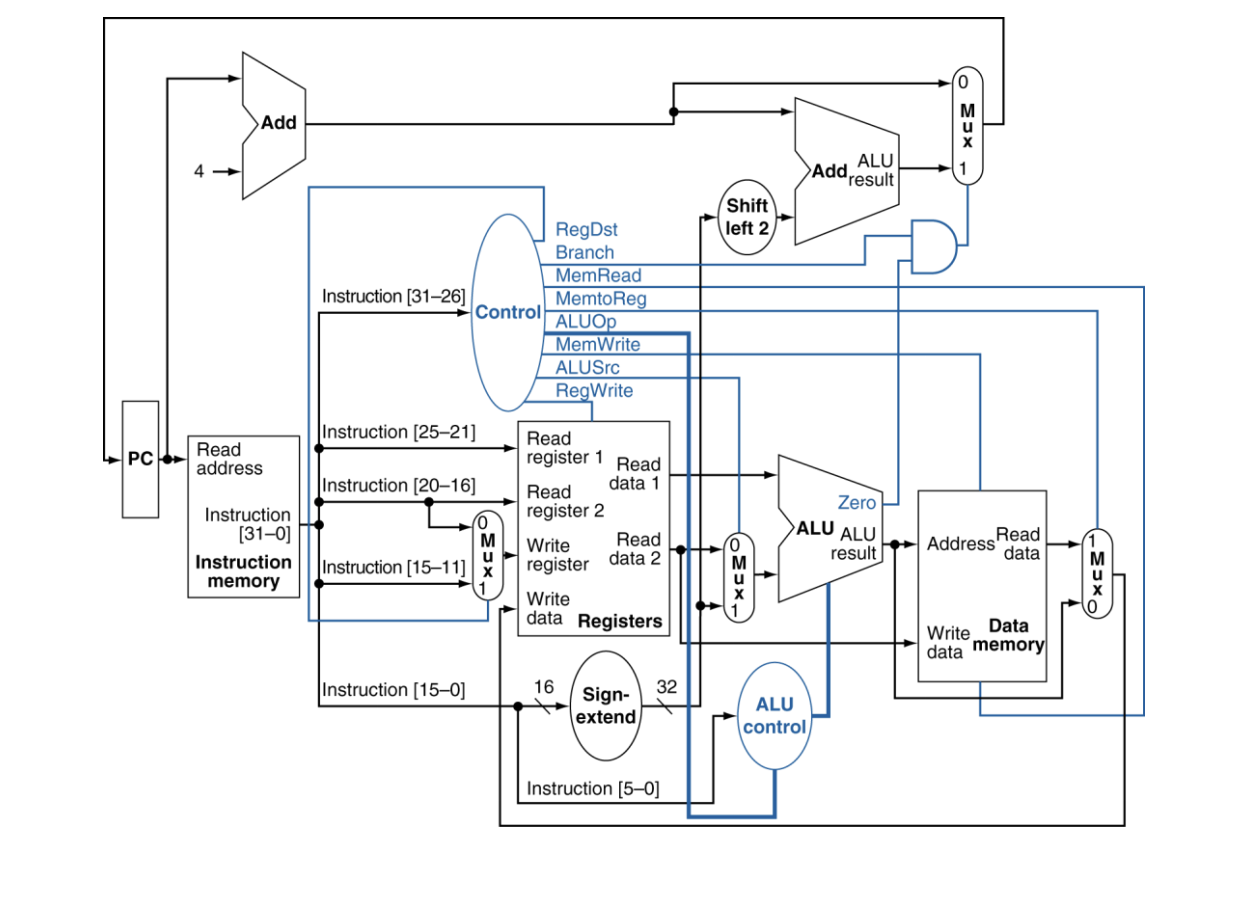

Appendix B: MIPS datapath (single cycle implementation):

Add (o 23 - ALU 4 - Add result Shift left 2 RegDst Branch Mem Read Instruction (31-26] MemtoReg Control ALUOP Mem Write ALUSrc RegWrite Instruction (25-21] PCI- Read address Instruction (20-16] Read register 1 Read Read data 1 register 2 Write Read Zero ALU ALU Instruction (31-0] Instruction memory 2x Read Address data result Instruction (1511] register data 2 Cx-39 * Write data Registers Write Data data memory Instruction (15-0] 16 32 Sign- extend ALU control Instruction [5-0]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts