Question: Really need help understanding how to solve the train circuit below. Inputs to the circuit (besides the Clk clock signal) are A and B. Y

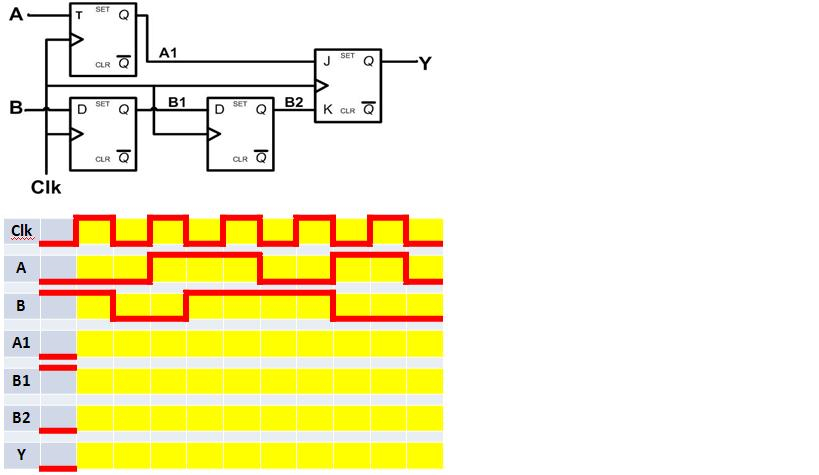

Really need help understanding how to solve the train circuit below. Inputs to the circuit (besides the Clk clock signal) are A and B. Y is the output, and A1, B1 and B2 are intermediate points within the circuit. All flip-flops used in this circuit are synchronous - that is, values are accepted on their inputs (and processed) when the clock signal is high, but results are not displayed on their Q and Q' outputs until the clock signal goes low, This isvery important in following the operation of the circuit!

Below the circuit diagram is a pulse train, with the trains for A, B and Clk filled in. Also filled in are the initial values for A1, B1, B2, and Y.

You should complete the pulse trains for A1, B1, B2 and Y and enter the sequences in the yellow area in the spaces provided below as groups of ten 1's and 0's (for example, 1100110000).

Recommendation on how to tackle this problem: Do the trains one at a time: do the entire left-to-right train for A1, followed by that for B1, then for B2, and finally for Y. If you try to do the first clock cycle for A1, B1, B2 and Y, and then move on to the next clock cycle, you will get hopelessly confused! Do not be distracted by all the trains. At any one time, you are looking at inputs from only one (or, in one case, two) other train, in addition to the clock signal. Examples: when working on A1, you need only look at signal A and the Clk signal. When working on Y, you have to look at the trains for A1 and B2, plus the Clk signal.

A T SET Qa A1 CLR CIk Clk A A1 B2 SET

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts