Question: ROB question two 2. ROB trace - dual issue Assume the following: Ten ROB slots. 1 integer Execution unit, 3 reservation stations, one cycle to

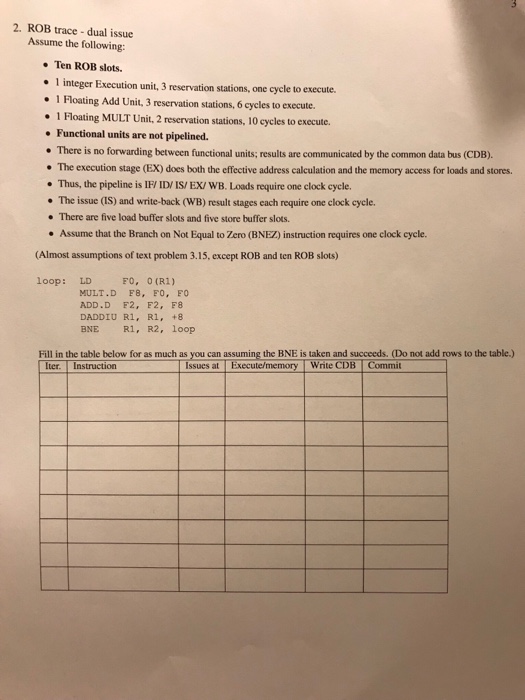

2. ROB trace - dual issue Assume the following: Ten ROB slots. 1 integer Execution unit, 3 reservation stations, one cycle to execute. 1 Floating Add Unit, 3 reservation stations, 6 cycles to execute. 1 Floating MULT Unit, 2 reservation stations, 10 cycles to execute. Functional units are not pipelined. There is no forwarding between functional units; results are communicated by the common data bus (CDB). The execution stage (EX) does both the effective address calculation and the memory access for loads and stores. Thus, the pipeline is IF/ ID/ IS, EX/ WH. Loads require one clock cycle. The issue (IS) and write-back (WB) result stages each require one clock cycle. There are five load buffer slots and five store buffer slots. e Assume that the Branch on Not Equal to Zero (BNEZ) instruction requires one clock cycle (Almost assumptions of text problem 3.15, except ROB and ten ROB slots) loop: LD FO, 0 (RI) MULT.D F8, FO, FO ADD.D F2, F2, F8 DADDIU Ri, Ri, +8 BNE R1, R2, loop Fill in the table below for as much as you can assuming the BNE is taken and succeeds. (Do not add rows to the table.) Iter. Instruction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts