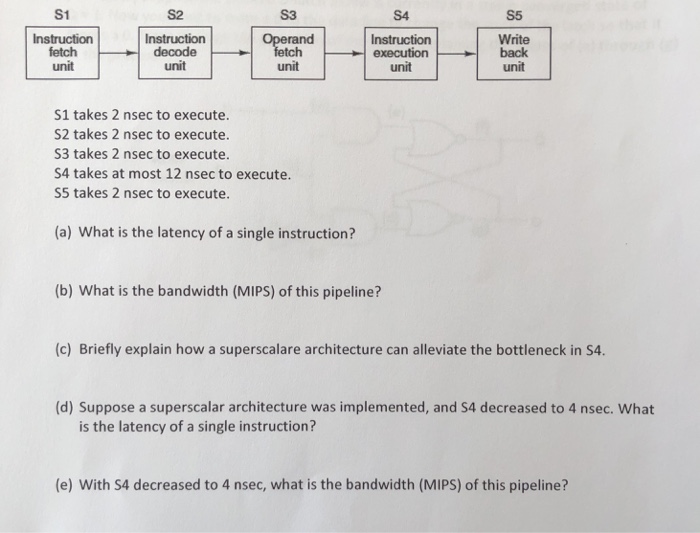

Question: S1 S2 Instruction decode S3 S4 Instruction fetch unit Instruction execution unit S5 Write unit erand back unit unit S1 takes 2 nsec to execute.

S1 S2 Instruction decode S3 S4 Instruction fetch unit Instruction execution unit S5 Write unit erand back unit unit S1 takes 2 nsec to execute. S2 takes 2 nsec to execute. S3 takes 2 nsec to execute. S4 takes at most 12 nsec to execute. S5 takes 2 nsec to execute. (a) What is the latency of a single instruction? (b) What is the bandwidth (MIPS) of this pipeline? (c) Briefly explain how a superscalare architecture can alleviate the bottleneck in S4. (d) Suppose a superscalar architecture was implemented, and S4 decreased to 4 nsec. What is the latency of a single instruction? (e) With S4 decreased to 4 nsec, what is the bandwidth (MIPS) of this pipeline

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts