Question: Show that the worst case delay through a nxn array of the type shown in Figure 9 . 6 b is 6 ( n -

Show that the worst case delay through a nxn array of the type shown in Figure b is n gate delays, as claimed in Section Array Multiplier

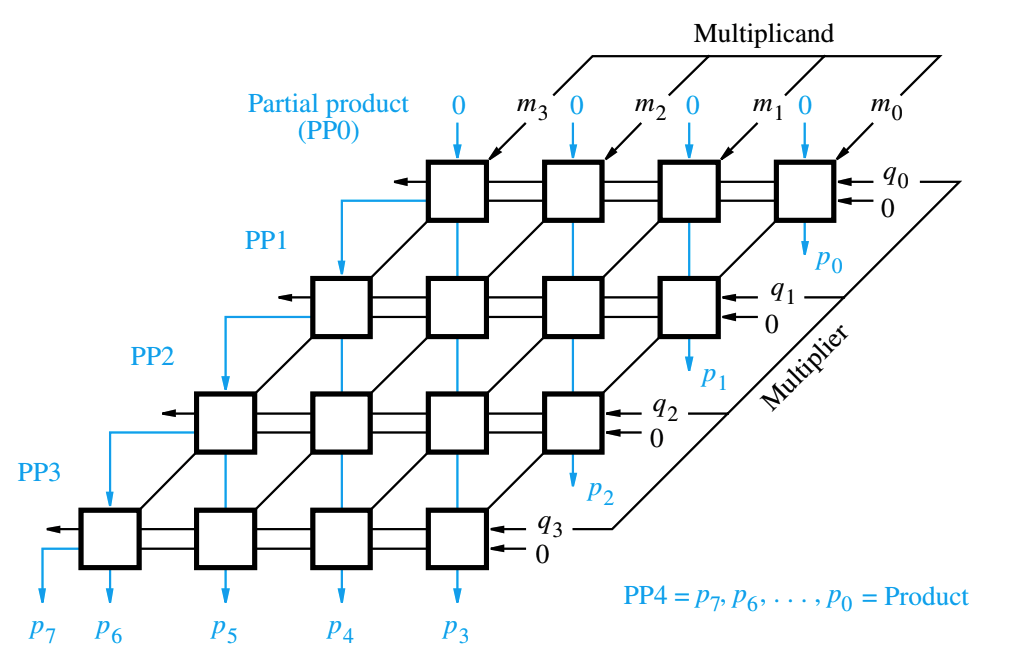

Binary multiplication of unsigned operands can be implemented in a combinational, two

dimensional, logic array, as shown in Figure b for the bit operand case. The main

component in each cell is a full adder, FA The AND gate in each cell determines whether a

multiplicand bit, mj is added to the incoming partialproduct bit, based on the value of the

multiplier bit, qi Each row i where i adds the multiplicand appropriately shifted

to the incoming partial product, PPi, to generate the outgoing partial product, PPi if

qi If qi PPi is passed vertically downward unchanged. PP is all s and PP is

the desired product. The multiplicand is shifted left one position per row by the diagonal

signal path. We note that the rowbyrow addition done in the array circuit differs from the

usual hand addition described previously, which is done columnbycolumn.

The worstcase signal propagation delay path is from the upper right corner of the

array to the highorder product bit output at the bottom left corner of the array. This critical

path consists of the staircase pattern that includes the two cells at the right end of each row, followed by all the cells in the bottom row. Assuming that there are two gate delays

from the inputs to the outputs of a fulladder block, FA the critical path has a total of

n gate delays, including the initial AND gate delay in all cells, for an n times n

arrray. In the first row of the array, no full adders are needed, because

the incoming partial product PP is zero. This has been taken into account in developing

the delay expression.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock