Question: Simulate a 2-way set associative 64-byte cache with 1-word blocks and LRU replacement. The following list of memory addresses is accessed in order: 4. 16,

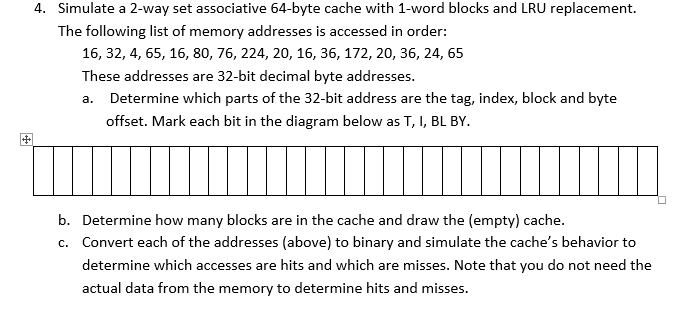

Simulate a 2-way set associative 64-byte cache with 1-word blocks and LRU replacement. The following list of memory addresses is accessed in order: 4. 16, 32, 4, 65, 16, 80, 76, 224, 20, 16, 36, 172, 20, 36, 24, 65 These addresses are 32-bit decimal byte addresses. a. Determine which parts of the 32-bit address are the tag, index, block and byte offset. Mark each bit in the diagram below as T, I, BL BY b. Determine how many blocks are in the cache and draw the (empty) cache. c. Convert each of the addresses (above) to binary and simulate the cache's behavior to determine which accesses are hits and which are misses. Note that you do not need the actual data from the memory to determine hits and misses

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts