Question: Sir plzz help this question Finish attem During a particular clock cycle, consider the CPU shown in the drawing Assume that the following initial data

Sir plzz help this question

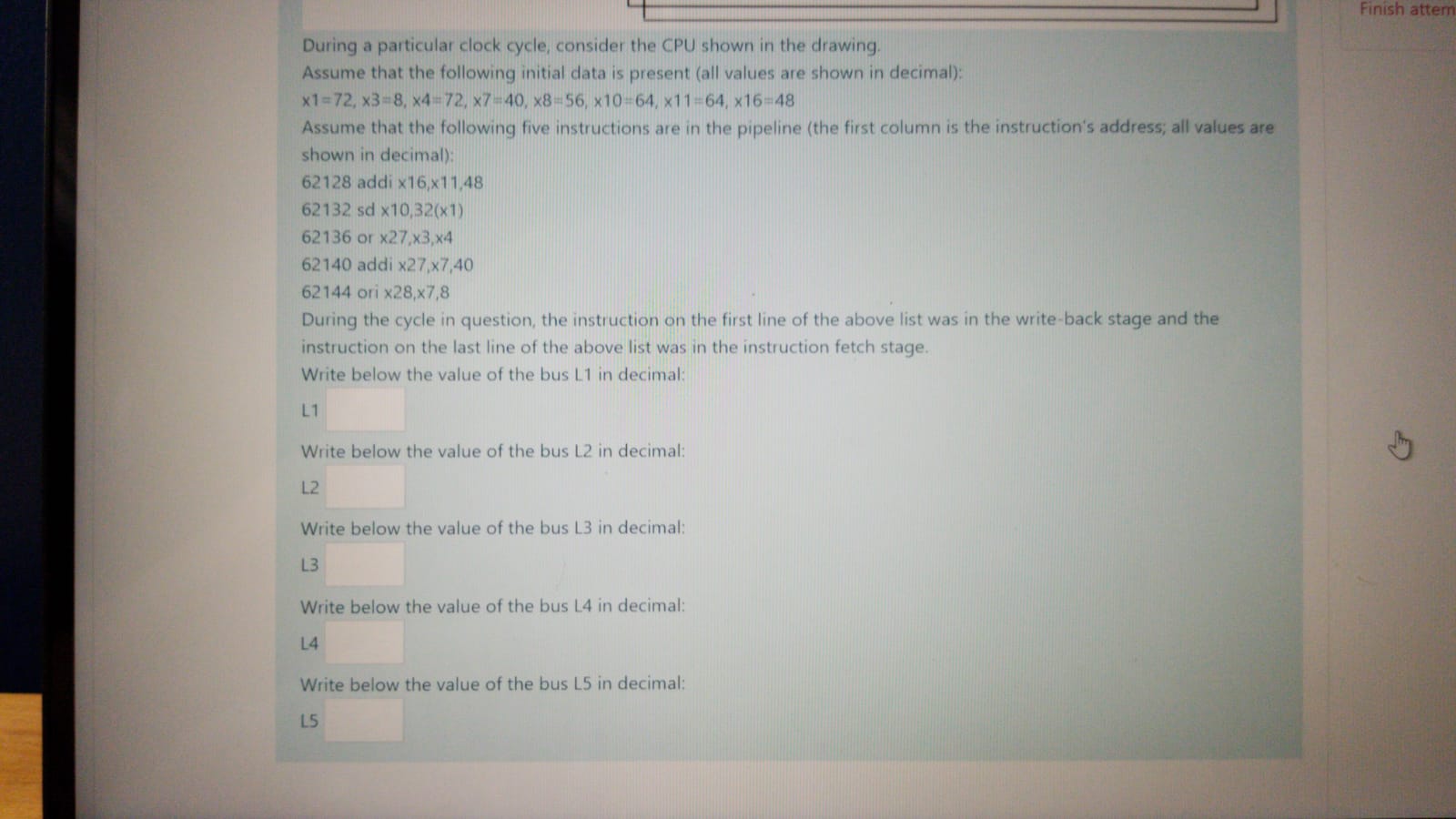

Finish attem During a particular clock cycle, consider the CPU shown in the drawing Assume that the following initial data is present (all values are shown in decimal): x1=72, x3-8, x4 72, x7-40, x8-56, x10-64, x11-64, x16=48 Assume that the following five instructions are in the pipeline (the first column is the instruction's address; all values are shown in decimal): 62128 addi x16,x11,48 62132 sd x10,32(x1) 62136 or x27,x3,x4 62140 addi x27,x7,40 62144 ori x28,x7,8 During the cycle in question, the instruction on the first line of the above list was in the write-back stage and the instruction on the last line of the above list was in the instruction fetch stage. Write below the value of the bus L1 in decimal: L1 Write below the value of the bus L2 in decimal: L2 Write below the value of the bus L3 in decimal: L3 Write below the value of the bus L4 in decimal: L4 Write below the value of the bus L5 in decimal; LS

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts