Question: solve problem 3 Only Problem 2 : Consider a dynamically scheduled single - issue processor that uses Tomasulo's algorithm with the following execution latencies: 3

solve problem Only Problem :

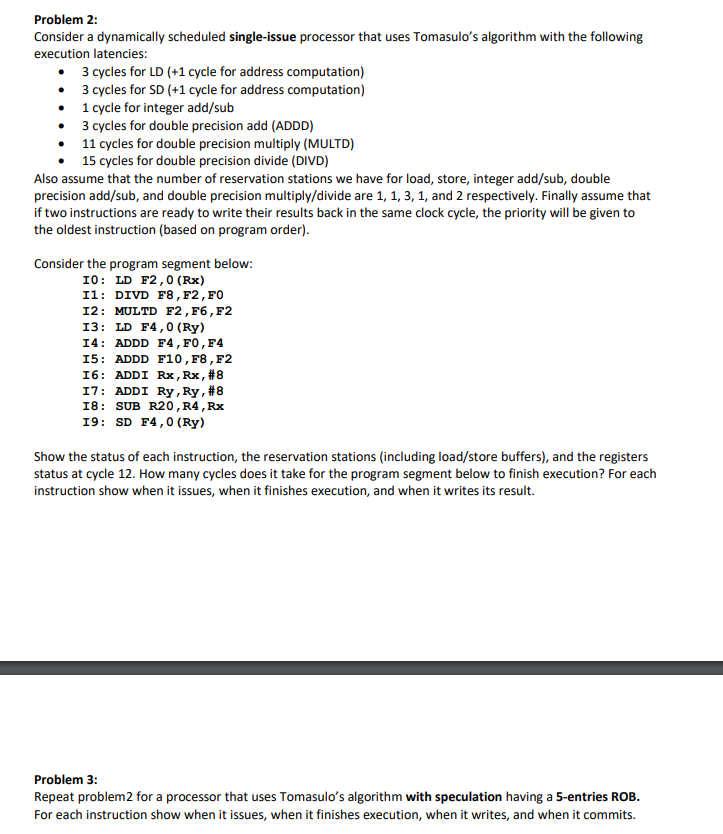

Consider a dynamically scheduled singleissue processor that uses Tomasulo's algorithm with the following

execution latencies:

cycles for LD cycle for address computation

cycles for SD cycle for address computation

cycle for integer addsub

cycles for double precision add ADDD

cycles for double precision multiply MULTD

cycles for double precision divide DIVD

Also assume that the number of reservation stations we have for load, store, integer addsub double

precision addsub and double precision multiplydivide are and respectively. Finally assume that

if two instructions are ready to write their results back in the same clock cycle, the priority will be given to

the oldest instruction based on program order

Consider the program segment below:

Show the status of each instruction, the reservation stations including loadstore buffers and the registers

status at cycle How many cycles does it take for the program segment below to finish execution? For each

instruction show when it issues, when it finishes execution, and when it writes its result.

Problem :

Repeat problem for a processor that uses Tomasulo's algorithm with speculation having a entries ROB.

For each instruction show when it issues, when it finishes execution, when it writes, and when it commits.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock