Question: Suppose we had a CPU design that can only do addq instructions as presented in the lecture, and we want to augment it to also

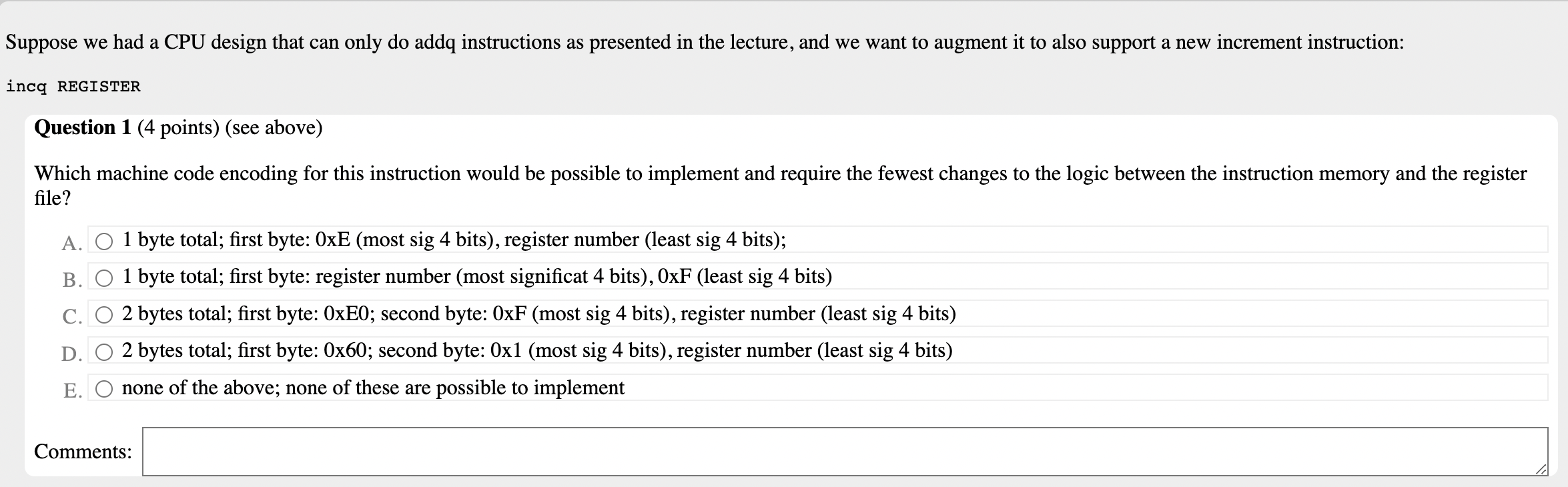

Suppose we had a CPU design that can only do addq instructions as presented in the lecture, and we want to augment it to also support a new increment instruction: incq REGISTER Question 1 (4 points) (see above) Which machine code encoding for this instruction would be possible to implement and require the fewest changes to the logic between the instruction memory and the register file? A. 1 byte total; first byte: 0xE (most sig 4 bits), register number (least sig 4 bits); B. 1 byte total; first byte: register number (most significat 4 bits), 0xF (least sig 4 bits) C. 2 bytes total; first byte: 0xE0; second byte: 0xF (most sig 4 bits), register number (least sig 4 bits) D. 2 bytes total; first byte: 0x60; second byte: 0x1 (most sig 4 bits), register number (least sig 4 bits) E. none of the above; none of these are possible to implement Comments

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts