Question: Task Breakdown 1 - D Flip - Flop You will create a simplified version of logic.ly ' s built - in D Flip - Flop,

Task Breakdown

D FlipFlop

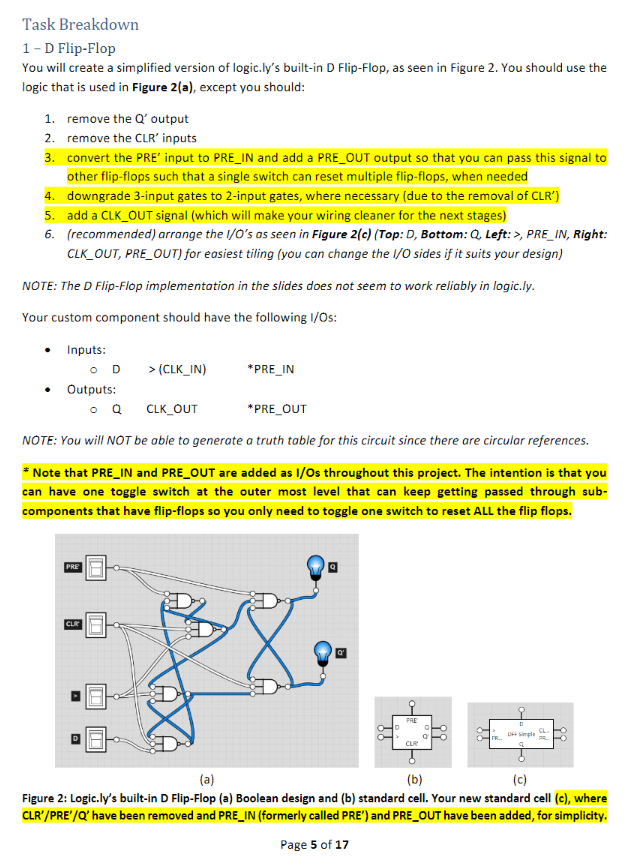

You will create a simplified version of logic.lys builtin D FlipFlop, as seen in Figure You should use the logic that is used in Figure a except you should:

remove the mathrmQprime output

remove the CLR inputs

convert the PRE' input to PREIN and add a PREOUT output so that you can pass this signal to other flipflops such that a single switch can reset multiple flipflops, when needed

downgrade input gates to input gates, where necessary due to the removal of CLR

add a CLKOUT signal which will make your wiring cleaner for the next stages

recommended arrange the IOs as seen in Figure cTop: D Bottom: Q Left: PREIN Right: CLKOUT, PREOUT for easiest tiling you can change the IO sides if it suits your design

NOTE: The D FlipFlop implementation in the slides does not seem to work reliably in logic.ly

Your custom component should have the following IOs:

Inputs:

D CLKINPREIN

Outputs:

Q CLKOUT PREOUT

NOTE: YOu will NOT be able to generate a truth table for this circuit since there are circular references.

Note that PREIN and PREOUT are added as IOs throughout this project. The intention is that you can have one toggle switch at the outer most level that can keep getting passed through subcomponents that have flipflops so you only need to toggle one switch to reset ALL the flip flops.

a

b

c

Figure : Logic.lys builtin D FlipFlop a Boolean design and b standard cell. Your new standard cell c where CLRPREQ have been removed and PREIN formerly called PRE' and PREOUT have been added, for simplicity.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock