Question: test_bench.v. //----------------------------------------------------------------------------- // Title : MIPS Pipelined Processor // Project : ECE 313 - Computer Organization //----------------------------------------------------------------------------- // File : mips_single.v // Author : John

test_bench.v.

//----------------------------------------------------------------------------- // Title : MIPS Pipelined Processor // Project : ECE 313 - Computer Organization //----------------------------------------------------------------------------- // File : mips_single.v // Author : John Nestor

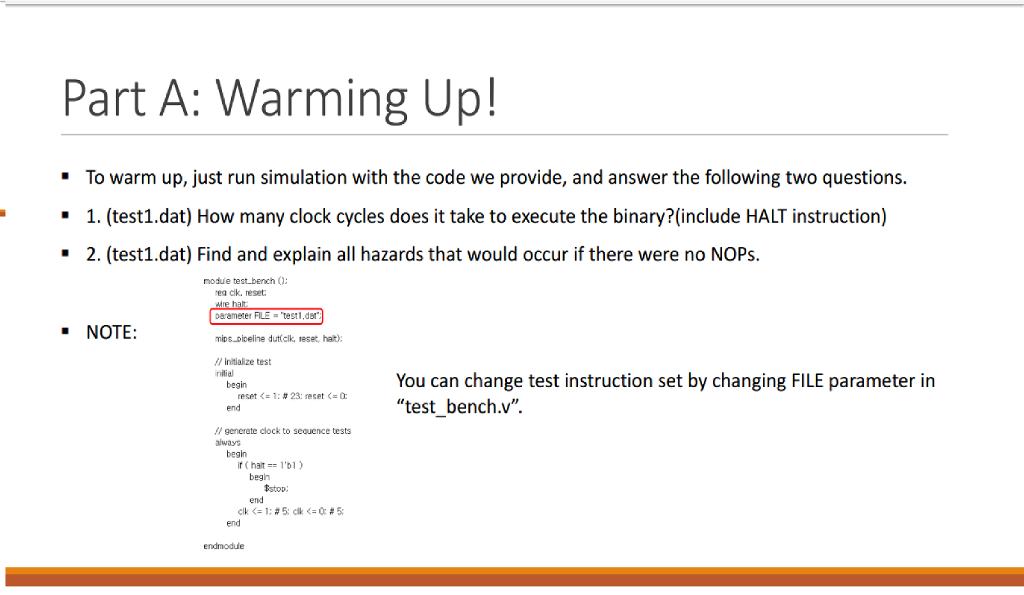

module test_bench (); reg clk, reset; wire halt; parameter FILE = "test1.dat"; mips_pipeline dut(clk, reset, halt);

// initialize test initial begin reset

// generate clock to sequence tests always begin if ( halt == 1'b1 ) begin $stop; end clk

endmodule

Part A: Warming Up! To warm up, just run simulation with the code we provide, and answer the following two questions. 1. (test1.dat) How many clock cycles does it take to execute the binary? de HALT instruction) 2. at) Find and explain all hazards that would occur if there were no NOPs. module test bench 0: reg ck, reset: Darameter FLE 'test 1.dBI NOTE mips pipeline dut(clk, reset, halt): initialize test initial You can change test instruction set by changing FILE parameter in begin reset 1: 23: reset test bench.v". generate clock to secuence tests always begin b1) if halt begin $stop. end Part A: Warming Up! To warm up, just run simulation with the code we provide, and answer the following two questions. 1. (test1.dat) How many clock cycles does it take to execute the binary? de HALT instruction) 2. at) Find and explain all hazards that would occur if there were no NOPs. module test bench 0: reg ck, reset: Darameter FLE 'test 1.dBI NOTE mips pipeline dut(clk, reset, halt): initialize test initial You can change test instruction set by changing FILE parameter in begin reset 1: 23: reset test bench.v". generate clock to secuence tests always begin b1) if halt begin $stop. end

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts