Question: The 2.5 GHz pipelined HotPipe processor has an ideal CPU CPI of 1 when there are no misses. It has a memory hierarchy that

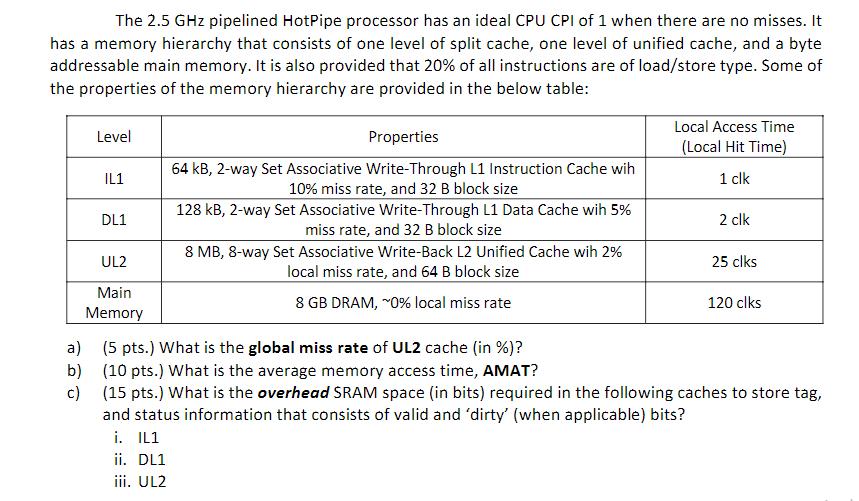

The 2.5 GHz pipelined HotPipe processor has an ideal CPU CPI of 1 when there are no misses. It has a memory hierarchy that consists of one level of split cache, one level of unified cache, and a byte addressable main memory. It is also provided that 20% of all instructions are of load/store type. Some of the properties of the memory hierarchy are provided in the below table: a) b) c) Level IL1 DL1 UL2 Main Memory Properties 64 kB, 2-way Set Associative Write-Through L1 Instruction Cache wih 10% miss rate, and 32 B block size 128 kB, 2-way Set Associative Write-Through L1 Data Cache wih 5% miss rate, and 32 B block size 8 MB, 8-way Set Associative Write-Back L2 Unified Cache wih 2% local miss rate, and 64 B block size 8 GB DRAM, ~0% local miss rate Local Access Time (Local Hit Time) 1 clk 2 clk 25 clks 120 clks (5 pts.) What is the global miss rate of UL2 cache (in %)? (10 pts.) What is the average memory access time, AMAT? (15 pts.) What is the overhead SRAM space (in bits) required in the following caches to store tag, and status information that consists of valid and 'dirty' (when applicable) bits? i. IL1 ii. DL1 iii. UL2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts