Question: The 4 GHz pipelined Citrus processor has an ideal CPU CPI of 2 when there are no misses. It has a memory hierarchy that consists

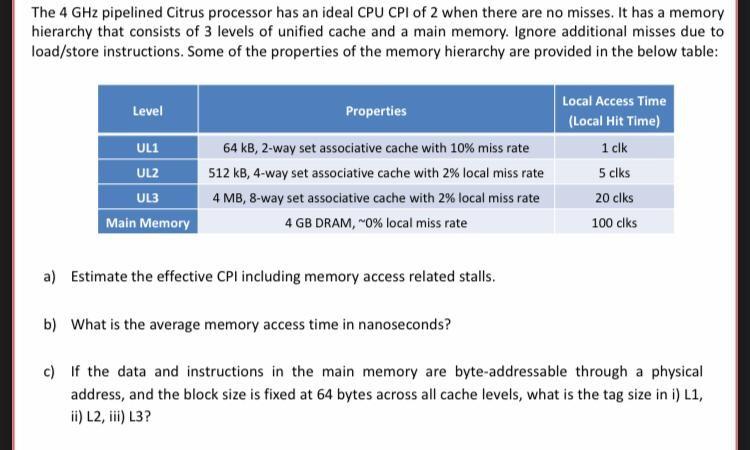

The 4 GHz pipelined Citrus processor has an ideal CPU CPI of 2 when there are no misses. It has a memory hierarchy that consists of 3 levels of unified cache and a main memory. Ignore additional misses due to load/store instructions. Some of the properties of the memory hierarchy are provided in the below table: Level Properties UL1 ULZ UL3 Main Memory 64 kB, 2-way set associative cache with 10% miss rate 512 KB, 4-way set associative cache with 2% local miss rate 4 MB, 8-way set associative cache with 2% local miss rate 4 GB DRAM, -0% local miss rate Local Access Time (Local Hit Time) 1 clk 5 clks 20 clks 100 clks a) Estimate the effective CPl including memory access related stalls. b) What is the average memory access time in nanoseconds? c) If the data and instructions in the main memory are byte-addressable through a physical address, and the block size is fixed at 64 bytes across all cache levels, what is the tag size in i) L1, ii) L2, iii) L3

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts