Question: The answers are given. Please explain the process, particularly the beginning, and why we are using 1.4 There are many different design parameters that are

The answers are given. Please explain the process, particularly the beginning, and why we are using

The answers are given. Please explain the process, particularly the beginning, and why we are using

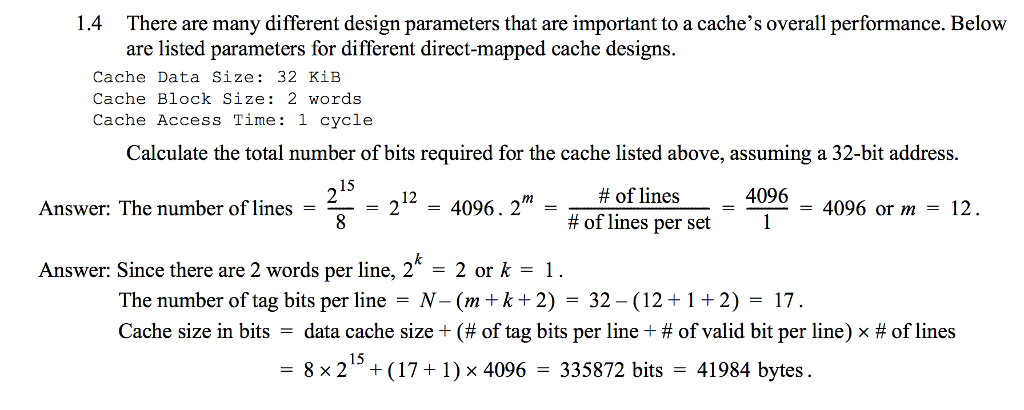

1.4 There are many different design parameters that are important to a cache's overall performance. Below are listed parameters for different direet-mapped cache designs. Cache Data Size: 32 KiB Cache Block Size: 2 words Cache Access Time: 1 cycle Calculate the total number of bits required for the cache listed above, assuming a 32-bit address. 15 # of lines # of lines per set 12 4096 Answer: The number oflines24096. 2" - 4096 or m-12 Answer: Since there are 2 words per line, 2* 2 or k The number of tag bits per line -N-(m+k+2) 32-(1212)17 Cache size in bits-data cache size + (# of tag bits per line + # of valid bit per line) x # of lines 15 8 x 2 + (17+ 1)x 4096 - 335872 bits - 41984 bytes

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts