Question: The execution cycles for various instructions are given in the following table. All units are pipelined. Loads and stores require the Integer ALU for address

The execution cycles for various instructions are given in the following table. All units are pipelined. Loads and stores require the Integer ALU for address generations and the load/store unit for accessing memory.

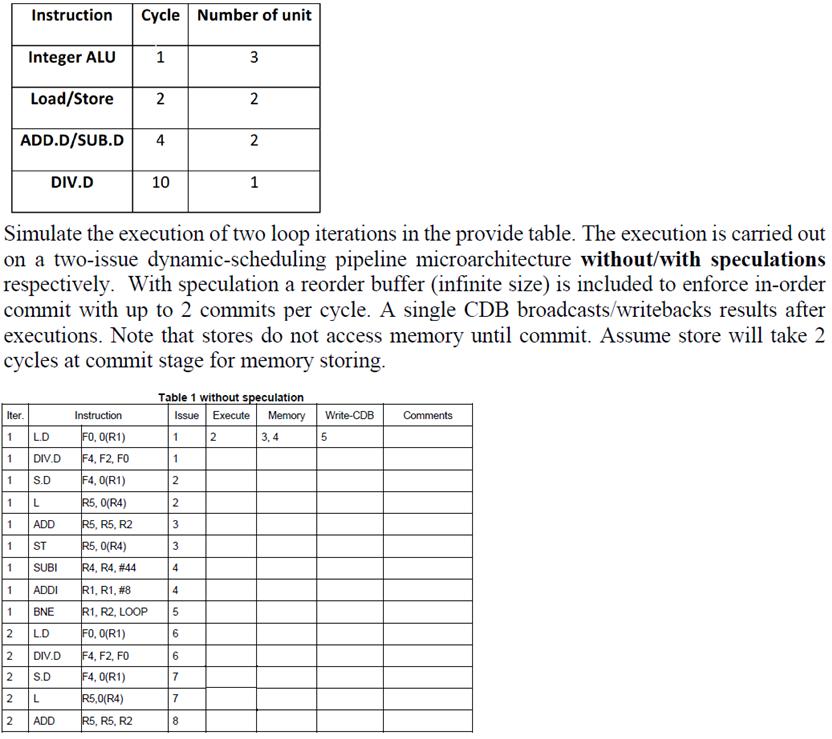

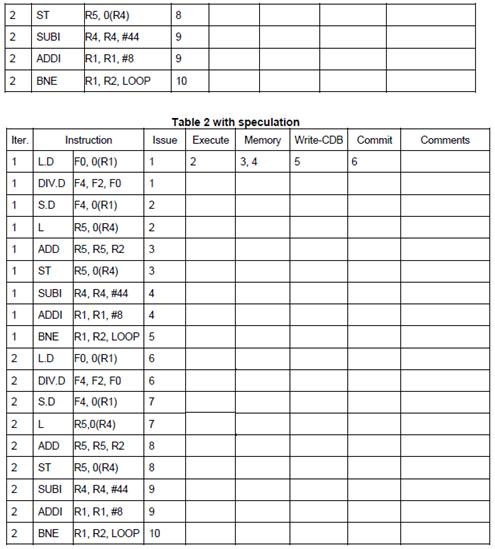

Instruction Cycle Number of unit Integer ALU 1 3 Load/Store 2 ADD.D/SUB.D 4 DIV.D 10 1 Simulate the execution of two loop iterations in the provide table. The execution is carried out on a two-issue dynamic-scheduling pipeline microarchitecture without/with speculations respectively. With speculation a reorder buffer (infinite size) is included to enforce in-order commit with up to 2 commits per cycle. A single CDB broadcasts/writebacks results after executions. Note that stores do not access memory until commit. Assume store will take 2 cycles at commit stage for memory storing. Table 1 without speculation Issue Execute Memory Write-CDB 2 Iter. Instruction Comments L.D FO, O(R1) 3, 4 5 DIV.D F4, F2, FO F4, 0(R1) 2 S.D L R5, O(R4) ADD R5, R5, R2 3 1 R5, O(R4) ST 3 SUBI R4, R4, #44 4 ADDI R1, R1, #8 4 R1, R2, LOOP FO, O(R1) 1 BNE 2 LD 6. 2 2 F4, F2, FO F4, 0(R1) R5,0(R4) DIV.D 6 S.D 7 2 7 ADD R5, R5, R2 8. 2. 2. 2.

Step by Step Solution

3.39 Rating (149 Votes )

There are 3 Steps involved in it

To simulate the execution of the loop iterations with and without speculation we need to understand the program sequence and execution cycles for each ... View full answer

Get step-by-step solutions from verified subject matter experts