Question: The figure below shows a memory cell A built using two cascaded inverters. Data input D contains the value to be written to the

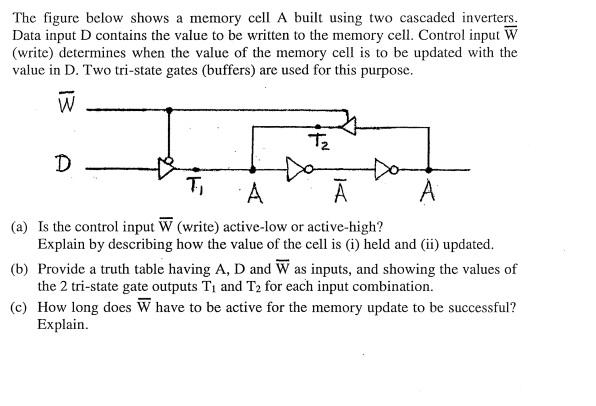

The figure below shows a memory cell A built using two cascaded inverters. Data input D contains the value to be written to the memory cell. Control input W (write) determines when the value of the memory cell is to be updated with the value in D. Two tri-state gates (buffers) are used for this purpose. W D T Tz A (a) Is the control input W (write) active-low or active-high? Explain by describing how the value of the cell is (i) held and (ii) updated. (b) Provide a truth table having A, D and W as inputs, and showing the values of the 2 tri-state gate outputs T1 and T2 for each input combination. (c) How long does W have to be active for the memory update to be successful? Explain.

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts