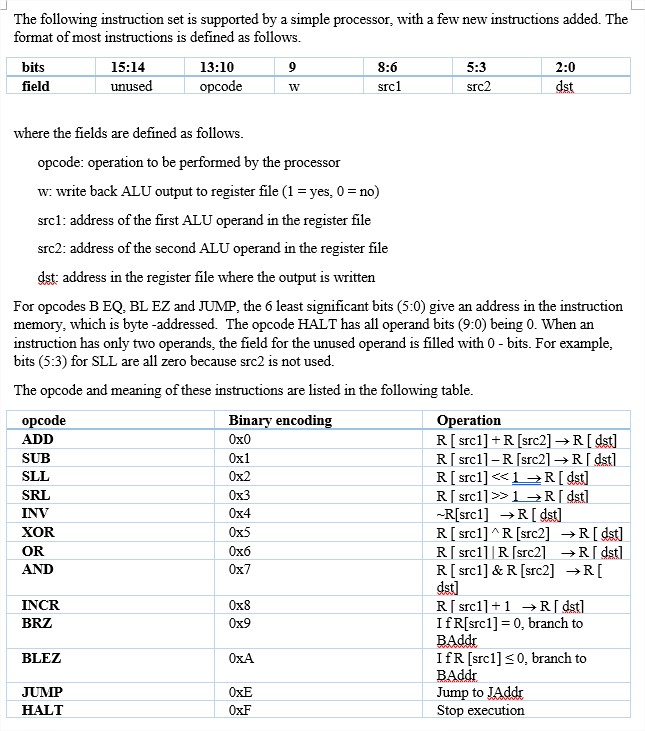

Question: The following instruction set is supported by a simple processor with a few new instructions added. The format of most instructions is defined as follows.

The following instruction set is supported by a simple processor with a few new instructions added. The format of most instructions is defined as follows. bits 15:14 13:10 9 8:o 5:3 2:0 unused opcode w Srci src dst field where the fields are defined as follows. opcode: operation to be performed by the processor w: write back ALU output to register file (1 yes, 0 src1: address of the first ALU operand in the register file src2: address of the second ALU operand in the register file dst: address in the register file where the output is written For opcodes B EQ, BLEZ and JUMP, the 6 least significant bits (5:0) give an address in the instruction memory, which is byte -addressed. The opcode HALT has all operand bits (9:0 being 0. When an instruction has only two operands, the field for the unused operand is filled with 0-bits. For example, bits (5:3) for SLL are all zero because src2 is not used. The opcode and meaning of these instructions are listed in the following table. opcode Binary encoding Operation ADD SUB 0x1 R Lsrcl src21 Rudsti SRL XOR. OR R Lsrcl AND 0x8 RLsrc11 1 RI dst INCR. IfRIsrcij 0, branch to BRZ IfR Src11 s0, branch to BLEZ 0XE p to Addr JUMP HALT Stop execution

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts