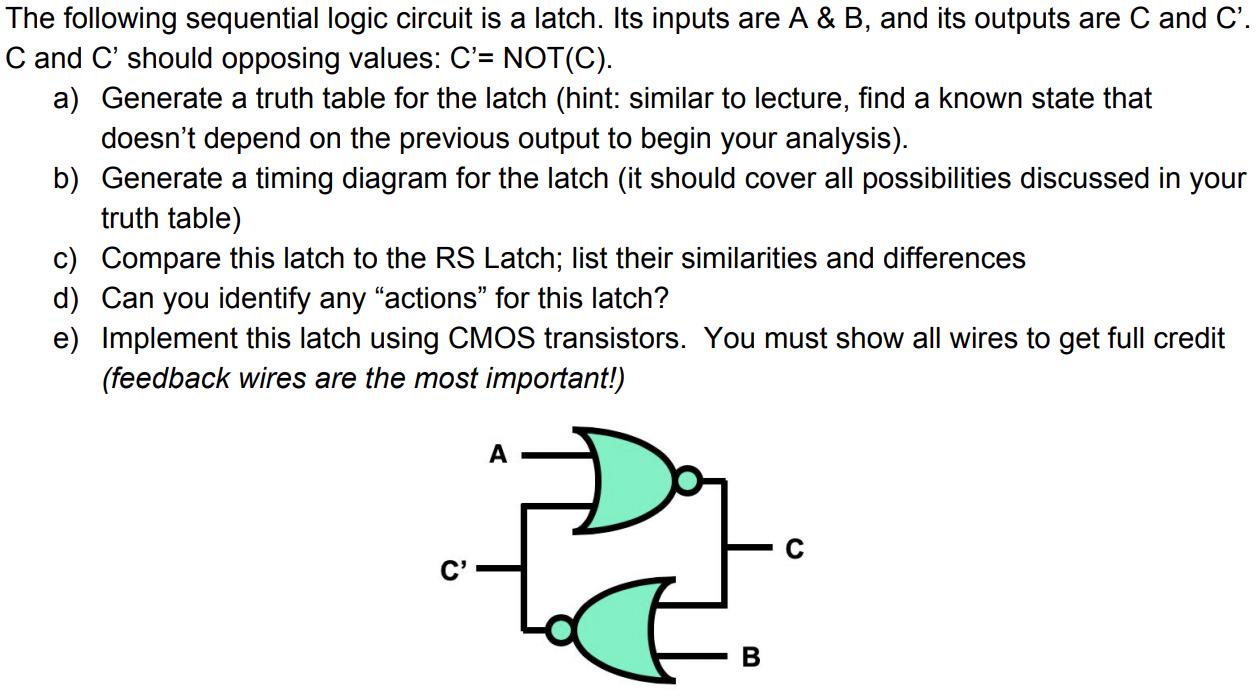

Question: The following sequential logic circuit is a latch. Its inputs are A & B, and its outputs are C and C'. C and C'

The following sequential logic circuit is a latch. Its inputs are A & B, and its outputs are C and C'. C and C' should opposing values: C'= NOT(C). a) Generate a truth table for the latch (hint: similar to lecture, find a known state that doesn't depend on the previous output to begin your analysis). b) Generate a timing diagram for the latch (it should cover all possibilities discussed in your truth table) c) Compare this latch to the RS Latch; list their similarities and differences d) Can you identify any "actions" for this latch? e) Implement this latch using CMOS transistors. You must show all wires to get full credit (feedback wires are the most important!) A D B

Step by Step Solution

3.56 Rating (153 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts