Question: Time left 2:12:32 Develop and test program employing modeling for 8 bit register employing flip flops, when the button BTNO (std_logic) is pressed register should

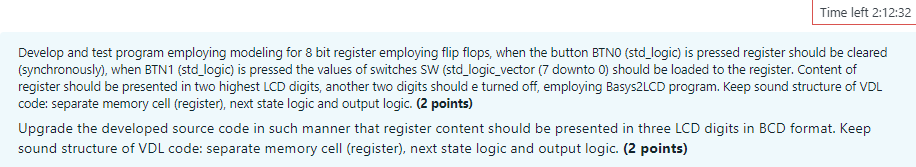

Time left 2:12:32 Develop and test program employing modeling for 8 bit register employing flip flops, when the button BTNO (std_logic) is pressed register should be cleared (synchronously), when BTN1 (std_logic) is pressed the values of switches SW (std_logic_vector (7 downto O) should be loaded to the register. Content of register should be presented in two highest LCD digits, another two digits should e turned off, employing Basys2LCD program. Keep sound structure of VDL code: separate memory cell (register), next state logic and output logic. (2 points) Upgrade the developed source code in such manner that register content should be presented in three LCD digits in BCD format. Keep sound structure of VDL code: separate memory cell (register), next state logic and output logic. (2 points) Time left 2:12:32 Develop and test program employing modeling for 8 bit register employing flip flops, when the button BTNO (std_logic) is pressed register should be cleared (synchronously), when BTN1 (std_logic) is pressed the values of switches SW (std_logic_vector (7 downto O) should be loaded to the register. Content of register should be presented in two highest LCD digits, another two digits should e turned off, employing Basys2LCD program. Keep sound structure of VDL code: separate memory cell (register), next state logic and output logic. (2 points) Upgrade the developed source code in such manner that register content should be presented in three LCD digits in BCD format. Keep sound structure of VDL code: separate memory cell (register), next state logic and output logic. (2 points)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts