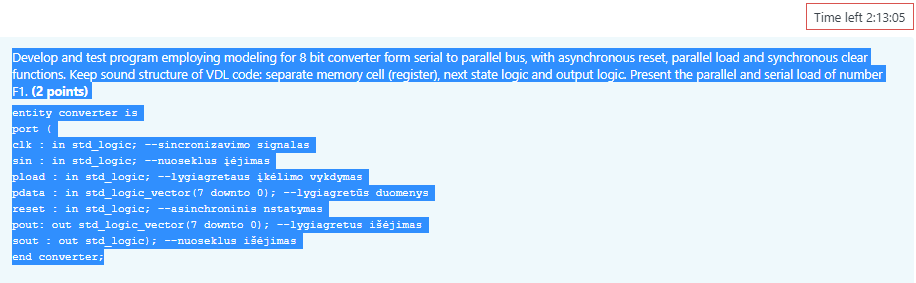

Question: Time left 2:13:05 Develop and test program employing modeling for 8 bit converter form serial to parallel bus, with asynchronous reset, parallel load and synchronous

Time left 2:13:05 Develop and test program employing modeling for 8 bit converter form serial to parallel bus, with asynchronous reset, parallel load and synchronous clear functions. Keep sound structure of VDL code: separate memory cell (register), next state logic and output logic Present the parallel and serial load of number F1. (2 points) entity converter is port clk : in std_logic; --sincronizavimo signalas sin : in std_logic; --nuoseklus jimas pload : in std_logic; --lygiagretaus klimo vykdymas pdata : in std_logic_vector (7 downto 0); --lygiagrets duomenys reset : in std_logic; --asinchroninis nstatymas pout: out std_logic_vector (7 downto 0); --lygiagretus ijimas sout : out std logic); --nuoseklus ijimas end converter; Time left 2:13:05 Develop and test program employing modeling for 8 bit converter form serial to parallel bus, with asynchronous reset, parallel load and synchronous clear functions. Keep sound structure of VDL code: separate memory cell (register), next state logic and output logic Present the parallel and serial load of number F1. (2 points) entity converter is port clk : in std_logic; --sincronizavimo signalas sin : in std_logic; --nuoseklus jimas pload : in std_logic; --lygiagretaus klimo vykdymas pdata : in std_logic_vector (7 downto 0); --lygiagrets duomenys reset : in std_logic; --asinchroninis nstatymas pout: out std_logic_vector (7 downto 0); --lygiagretus ijimas sout : out std logic); --nuoseklus ijimas end converter

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts