Question: To provide cache consistency in a Symmetric Multiprocessor (SMP) configuration, the data cache often supports a protocol known as MESI protocol. Consider a machine

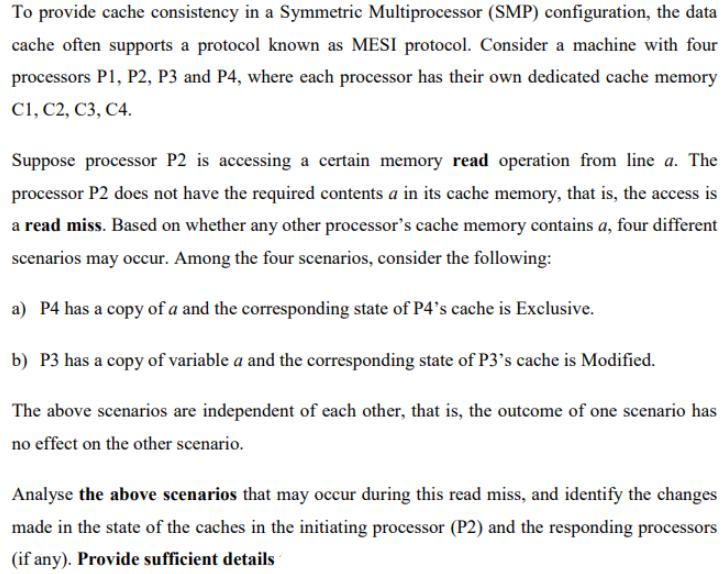

To provide cache consistency in a Symmetric Multiprocessor (SMP) configuration, the data cache often supports a protocol known as MESI protocol. Consider a machine with four processors P1, P2, P3 and P4, where each processor has their own dedicated cache memory C1, C2, C3, C4. Suppose processor P2 is accessing a certain memory read operation from line a. The processor P2 does not have the required contents a in its cache memory, that is, the access is a read miss. Based on whether any other processor's cache memory contains a, four different scenarios may occur. Among the four scenarios, consider the following: a) P4 has a copy of a and the corresponding state of P4's cache is Exclusive. b) P3 has a copy of variable a and the corresponding state of P3's cache is Modified. The above scenarios are independent of each other, that is, the outcome of one scenario has no effect on the other scenario. Analyse the above scenarios that may occur during this read miss, and identify the changes made in the state of the caches in the initiating processor (P2) and the responding processors (if any). Provide sufficient details

Step by Step Solution

3.48 Rating (161 Votes )

There are 3 Steps involved in it

In the MESI Modified Exclusive Shared Invalid protocol used in SMP configurations lets consider the ... View full answer

Get step-by-step solutions from verified subject matter experts