Upon completion of this lab you should be able to create and test a design using...

Fantastic news! We've Found the answer you've been seeking!

Question:

Transcribed Image Text:

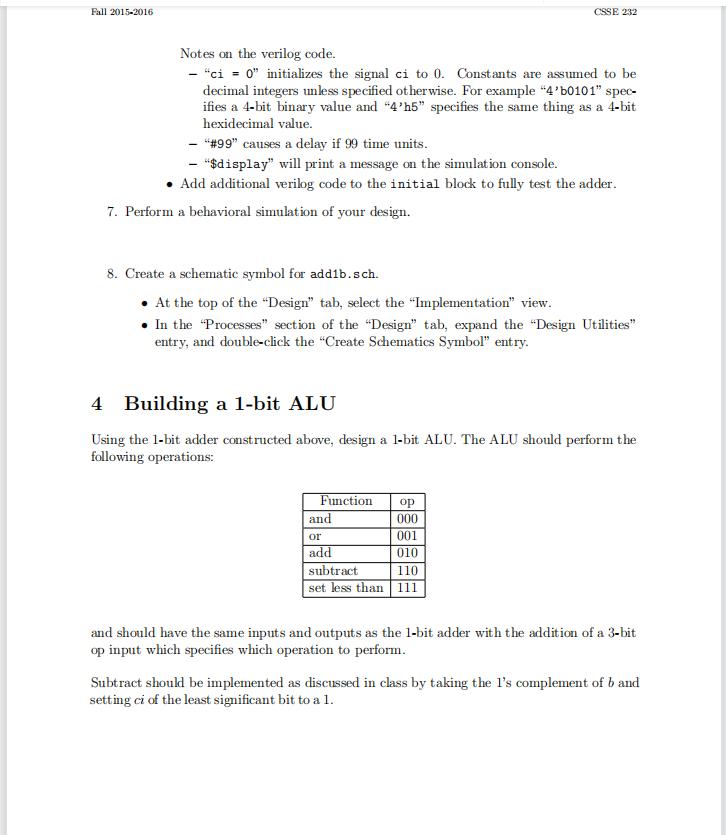

Upon completion of this lab you should be able to create and test a design using the Xilinx ISE tools. 2 General This lab willl guide you through building and testing an ALU. We will follow the "Top-down design: bottom-up implementation" approach. 3 Building a 1-bit adder 1. Start Xilinx ISE 14.7 2. Select File→New Project... to open the "New Project Wizard." (a) In the "Create New Project" dialog: i. enter "alu" for the "Name", ii. choose the "Location", iii. CRITICAL: change the "Working directory" to "the location selected above/work", iv. select "Schematic" as the "Top-Level Source Type", and v. click "Next". (b) In the "Project Settings" dialog, enter the following properties: • Family: Spartan3E Device: XC3S500E Package: FG320 Speed: -4 • Synthesis Tool: XST (VHDL/Verilog) Fall 2015-2016 Simulator: ISim (VHDL/Verilog) • Prefered Language: Verilog and click "Next". (c) Click "Finish" in the "Project Summary" dialog. Note: You can change the project properties by right clicking on the device (i.e. xc3s500e-4fg320) in the "Hierarchy" section of the "Design" tab and selecting "De- sign Properties..." CSSE 232 3. Add a new source to the project. There are a number of ways that you can do this: • Right click on the device in the "Hierarchy" section of the "Design" tab and select "New Source..." • Select Project New Source... . Click the "New Source" icon in the toolbar. The "New Source Wizard" should appear. (a) In the "Select Source Type" dialog, select "Schematic", enter "add1b" as the "File name:" and click "Next". (b) In the "Summary" dialog, click "Finish". 4. In add1b.sch implement the following logic: r=ci-a-b+ci-a-l and -b+ci·a·b+ci-a-b (1) co= ci-a +ci-b+a·b, (2) where a and b are inputs to the adder, ci is the carry-in, r is the result, and co is the carry-out. • You should build the logic using and gates, or gates and inverters, which are all available in the symbols tab. • To search for a symbol, type the first part of a symbols name in the "Symbol Name Filter". • To add a symbol to your schematic, select a symbol in the symbol pane (this will switch to "add symbol" mode) and click in the schematic. Clicking again will place another symbol. Pushing "Esc" or right-clicking will cancel "add symbol" mode. • To connect the symbols click the "Add Wire" icon in the toolbar. Click and drag in the schematic to specify a wire between a single pair of points. Use clicks (no drag) to specify a sequence of connected wire points. Double click will terminate the sequence. • To add input and output pins click the "Add I/O Marker" icon in the toolbar. • To name the input and output pins, click the "Add Net Name" icon in the toolbar and fill in "Name" in the "Options" pane. • To check your schematic click "Check Schematic" from the toolbar. • Try to create your own design. However, if you get stuck, you can take a look at mine. 5. Make sure addib. sch is set as the top level module and synthesize it. Correct any errors. 6. Create a testbench. (a) At the top of the "Design" tab, select the "Simulation" view. (b) Add a new source to the project. For source type select "Verilog Test Fixture" and filename add1b_tb_0. • On the "Associate Source" dialog select "add1b" and click "Next". Click "Finish". (c) In the "Hierarchy" section of the "Design" tab, double-click on add1b_tb_0. vand examine the test bench. (d) Edit the verilog code to fully test the adder. • Feel free to change the module name to something more reasonable. I used add1b_tb_0. 15 October 2015 Delete the following section. 'ifdef auto_init initial begin ci = 0; b = 0; a = 0; 'endif Add the following section in its place. initial begin ci = 0; b = 0; a = 0; // Wait 100ns for the simulator to finish initializing # 100; a = 1; #1; if ((r == 1) && (co == 0)) $display("okay 1"); $display("fail 1"); end else Page 3 Fall 2015-2016 Notes on the verilog code. - "ci = 0" initializes the signal ci to 0. Constants are assumed to be decimal integers unless specified otherwise. For example "4'b0101" spec- ifies a 4-bit binary value and "4'h5" specifies the same thing as a 4-bit hexidecimal value. - "# 99" causes a delay if 99 time units. - "$display" will print a message on the simulation console. Add additional verilog code to the initial block to fully test the adder. 7. Perform a behavioral simulation of your design. 8. Create a schematic symbol for add1b.sch. At the top of the "Design" tab, select the "Implementation" view. . In the Processes" section of the "Design" tab, expand the "Design Utilities" entry, and double-click the "Create Schematics Symbol" entry. CSSE 232 4 Building a 1-bit ALU Using the 1-bit adder constructed above, design a 1-bit ALU. The ALU should perform the following operations: Function and or add op 000 001 010 subtract 110 set less than 111 and should have the same inputs and outputs as the 1-bit adder with the addition of a 3-bit op input which specifies which operation to perform. Subtract should be implemented as discussed in class by taking the I's complement of b and setting ci of the least significant bit to a 1. Fall 2015-2016 1. Create a new schematic named alulb.sch and enter your design. 2. Create a new testbench named alulb_tb_0. v to test your design. CSSE 232 3. Perform a behavioral simulation of your design. Verify correct results. Modify your design if necessary 4. Create a symbol for aluib.sch. 5 Building a 4-bit ALU Using the 1-bit alu constructed above, design a 4-bit ALU. In addition to the basic operations performed by the 1-bit ALU, the 4-bit ALU should have an overflow detector and a zero detector. Be sure finish implementing subtract and set less than. Your 4-bit ALU should have 2, 4-bit inputs, a and b, a 3-bit input op, a 4-bit output r, and 2 1-bit outputs, zero and ovfl. 1. Create a new schematic named alu. sch and enter your design. 2. Create a new testbench named alu_tb_0.v to test your design. 3. Perform a behavioral simulation of your design. Verify correct results. Modify your design if necessary Upon completion of this lab you should be able to create and test a design using the Xilinx ISE tools. 2 General This lab willl guide you through building and testing an ALU. We will follow the "Top-down design: bottom-up implementation" approach. 3 Building a 1-bit adder 1. Start Xilinx ISE 14.7 2. Select File→New Project... to open the "New Project Wizard." (a) In the "Create New Project" dialog: i. enter "alu" for the "Name", ii. choose the "Location", iii. CRITICAL: change the "Working directory" to "the location selected above/work", iv. select "Schematic" as the "Top-Level Source Type", and v. click "Next". (b) In the "Project Settings" dialog, enter the following properties: • Family: Spartan3E Device: XC3S500E Package: FG320 Speed: -4 • Synthesis Tool: XST (VHDL/Verilog) Fall 2015-2016 Simulator: ISim (VHDL/Verilog) • Prefered Language: Verilog and click "Next". (c) Click "Finish" in the "Project Summary" dialog. Note: You can change the project properties by right clicking on the device (i.e. xc3s500e-4fg320) in the "Hierarchy" section of the "Design" tab and selecting "De- sign Properties..." CSSE 232 3. Add a new source to the project. There are a number of ways that you can do this: • Right click on the device in the "Hierarchy" section of the "Design" tab and select "New Source..." • Select Project New Source... . Click the "New Source" icon in the toolbar. The "New Source Wizard" should appear. (a) In the "Select Source Type" dialog, select "Schematic", enter "add1b" as the "File name:" and click "Next". (b) In the "Summary" dialog, click "Finish". 4. In add1b.sch implement the following logic: r=ci-a-b+ci-a-l and -b+ci·a·b+ci-a-b (1) co= ci-a +ci-b+a·b, (2) where a and b are inputs to the adder, ci is the carry-in, r is the result, and co is the carry-out. • You should build the logic using and gates, or gates and inverters, which are all available in the symbols tab. • To search for a symbol, type the first part of a symbols name in the "Symbol Name Filter". • To add a symbol to your schematic, select a symbol in the symbol pane (this will switch to "add symbol" mode) and click in the schematic. Clicking again will place another symbol. Pushing "Esc" or right-clicking will cancel "add symbol" mode. • To connect the symbols click the "Add Wire" icon in the toolbar. Click and drag in the schematic to specify a wire between a single pair of points. Use clicks (no drag) to specify a sequence of connected wire points. Double click will terminate the sequence. • To add input and output pins click the "Add I/O Marker" icon in the toolbar. • To name the input and output pins, click the "Add Net Name" icon in the toolbar and fill in "Name" in the "Options" pane. • To check your schematic click "Check Schematic" from the toolbar. • Try to create your own design. However, if you get stuck, you can take a look at mine. 5. Make sure addib. sch is set as the top level module and synthesize it. Correct any errors. 6. Create a testbench. (a) At the top of the "Design" tab, select the "Simulation" view. (b) Add a new source to the project. For source type select "Verilog Test Fixture" and filename add1b_tb_0. • On the "Associate Source" dialog select "add1b" and click "Next". Click "Finish". (c) In the "Hierarchy" section of the "Design" tab, double-click on add1b_tb_0. vand examine the test bench. (d) Edit the verilog code to fully test the adder. • Feel free to change the module name to something more reasonable. I used add1b_tb_0. 15 October 2015 Delete the following section. 'ifdef auto_init initial begin ci = 0; b = 0; a = 0; 'endif Add the following section in its place. initial begin ci = 0; b = 0; a = 0; // Wait 100ns for the simulator to finish initializing # 100; a = 1; #1; if ((r == 1) && (co == 0)) $display("okay 1"); $display("fail 1"); end else Page 3 Fall 2015-2016 Notes on the verilog code. - "ci = 0" initializes the signal ci to 0. Constants are assumed to be decimal integers unless specified otherwise. For example "4'b0101" spec- ifies a 4-bit binary value and "4'h5" specifies the same thing as a 4-bit hexidecimal value. - "# 99" causes a delay if 99 time units. - "$display" will print a message on the simulation console. Add additional verilog code to the initial block to fully test the adder. 7. Perform a behavioral simulation of your design. 8. Create a schematic symbol for add1b.sch. At the top of the "Design" tab, select the "Implementation" view. . In the Processes" section of the "Design" tab, expand the "Design Utilities" entry, and double-click the "Create Schematics Symbol" entry. CSSE 232 4 Building a 1-bit ALU Using the 1-bit adder constructed above, design a 1-bit ALU. The ALU should perform the following operations: Function and or add op 000 001 010 subtract 110 set less than 111 and should have the same inputs and outputs as the 1-bit adder with the addition of a 3-bit op input which specifies which operation to perform. Subtract should be implemented as discussed in class by taking the I's complement of b and setting ci of the least significant bit to a 1. Fall 2015-2016 1. Create a new schematic named alulb.sch and enter your design. 2. Create a new testbench named alulb_tb_0. v to test your design. CSSE 232 3. Perform a behavioral simulation of your design. Verify correct results. Modify your design if necessary 4. Create a symbol for aluib.sch. 5 Building a 4-bit ALU Using the 1-bit alu constructed above, design a 4-bit ALU. In addition to the basic operations performed by the 1-bit ALU, the 4-bit ALU should have an overflow detector and a zero detector. Be sure finish implementing subtract and set less than. Your 4-bit ALU should have 2, 4-bit inputs, a and b, a 3-bit input op, a 4-bit output r, and 2 1-bit outputs, zero and ovfl. 1. Create a new schematic named alu. sch and enter your design. 2. Create a new testbench named alu_tb_0.v to test your design. 3. Perform a behavioral simulation of your design. Verify correct results. Modify your design if necessary

Expert Answer:

Related Book For

Financial Analysis with Microsoft Excel

ISBN: 978-1285432274

7th edition

Authors: Timothy R. Mayes, Todd M. Shank

Posted Date:

Students also viewed these organizational behavior questions

-

An exploration submarine should be able to go 4000 m down in the ocean. If the ocean density is 1020 kg/m3 what is the maximum pressure on the submarine hull?

-

An exploration submarine should be able to go 4000 m down in the ocean. If the ocean density is 1020 kg/m3 what is the maximum pressure on the submarine hull?

-

An emergency drain pump should be able to pump 0.1 m3/s liquid water at 15C, 10 m vertically up delivering it with a velocity of 20 m/s. It is estimated that the pump, pipe and nozzle have a combined...

-

Copper Industries (a sole proprietorship) sold three 1231 assets during 2015. Data on these property dispositions are as follows: a. Determine the amount and the character of the recognized gain or...

-

Omni Technology Holding Company has the following three affiliates: a. Which affiliate has the highest return on sales? b. Which affiliate has the lowest return on assets? c. Which affiliate has the...

-

Why is the equity method sometimes described as a one-line consolidation? Consider both the balance sheet and the income statement in your response.

-

Priscilla Webster was dining at her favorite Massachusetts seafood restaurant when matters went horribly wrong. She began choking on a fishbone that had been lurking in her seafood chowder. After a...

-

Fallon Company uses flexible budgets to control its selling expenses. Monthly sales are expected to range from $170,000 to $200,000. Variable costs and their percentage relationship to sales are...

-

Household income in marketing surveys is often reported in brackets: for example, under $15,000, $15,000$25,000, ... , over $95,000. (a) Suppose that household income is the outcome variable in a...

-

Eli Lilly owns the patent to Xigris, which is the only approved drug for the treatment of sepsis. Sepsis is a severe illness caused by a bacterial infection, which may lead to the failure of multiple...

-

Which of the following results in a decrease in the investment account when applying the equity method? A. Share of gross profit on intra-entity inventory sales for the current year. B. Net income of...

-

The Wilson Company is considering the purchase of a new warehouse. Wilson can borrow $78,000 from the bank to make the purchase. He will be required to make monthly payments of $2,234. How long will...

-

Consider the quadratic function y = -x+6x-5. What do we know about the graph of this quadratic equation, based on its formula? The vertex is (3,4) and it opens upward. The vertex is (-3,-32) and it...

-

Supervisor: "We have 81% of our team here today and we have 16 team members." Employee: "So, __________ members are missing today.

-

Consider that you have decided to quantify many of the aspects required for financial planning on a personal basis. Accordingly, using your age as of the first day of next month, make all the...

-

As we reflect on the topic of leadership we have wrestled with a few theories these past few weeks. Our readings seem to place some of these theories into categories or boxes to help us better...

-

K Sketch the region of integration, reverse the order of integration, and evaluate the integral. 42 +1 A. Choose the correct sketch below that describes the region R from the double integral. dy dx x...

-

Organizations are increasing their use of personality tests to screen job applicants. What are some of the advantages and disadvantages of this approach? What can managers do to avoid some of the...

-

Upon starting your new job after college, you've been confronted with selecting the investments for your 401(k) retirement plan. You have four choices for investing your money: A money market fund...

-

Your five-year-old daughter has just announced that she would like to attend college. The College Board has reported that the average cost of tuition, room, board, and other expense at public...

-

You are considering an investment in the stock market and have identified two potential stocks (XYZ and ABC) to purchase. The historical returns for the past five years are shown in the table below....

-

In an efficient market, the change in a companys share price is most likely the result of: A. Insiders private information. B. The previous days change in stock price. C. New information coming into...

-

Regulation that restricts some investors from participating in a market will most likely: A. Impede market efficiency. B. Not affect market efficiency. C. Contribute to market efficiency.

-

Which of the following regulations will most likely contribute to market efficiency? Regulatory restrictions on: A. Short selling. B. Foreign traders. C. Insiders trading with nonpublic information.

Study smarter with the SolutionInn App