Question: urgent CISC 3310 MWO 6. A general purpose processor repeatedly executes three (major) seps (6A) input, compile, and output (6C) Read, process, and write 60)

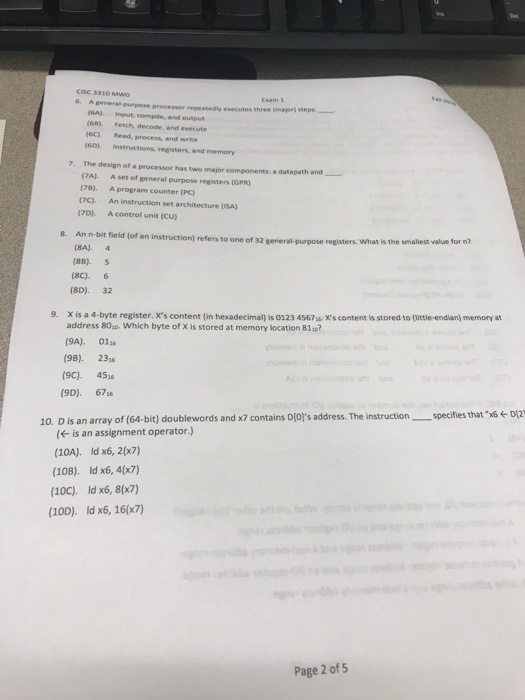

CISC 3310 MWO 6. A general purpose processor repeatedly executes three (major) seps (6A) input, compile, and output (6C) Read, process, and write 60) instructions, registers, and memory 7. The design of a processor has two major components: a datapath and_ (7A) Aset of general purpose registers (GPR) (78) A program counter (Pc) (7C). An instruction set architecture (ISA) A control unit (CU) (70 8. An n-bit field (of an instruction) refers to one of 32 general-purpose registers. What is the smallest value or n? (8A). 4 (8B). S (SC). 6 (8D). 32 X is a 4-byte register. x's content (in hexadecimal) is 0123 4567%, es contentis stored to titteendian) memory at address 80se. Which byte of X is stored at memory location 811? (9A). 01 (98). 23 (9C). 451 9. (9D). 67s6 10. D is an array of (64-bit) doublewords and x7 contains Dol's address. The instructionspecifies that "6DI2 is an assignment operator.) (10A). ld x6, 2(x7) (10B). Id x6, 4(x7) (10c). ld x6, 8(x7) (10D). Id x6, 16(x7) Page 2 of 5

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts