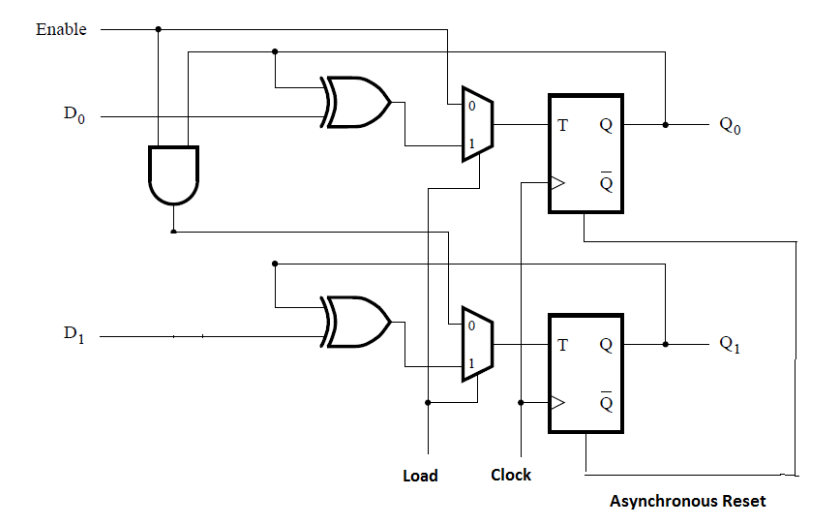

Question: Use the T flip flop design to write structural VHDL code for the two bit synchronous counter with parallel load and asynchronous reset. The circuit

Use the T flip flop design to write structural VHDL code for the two bit synchronous

counter with parallel load and asynchronous reset. The circuit is provided below. Write its SINGLE

test bench that cover following cases in the same order:

i.

Enable = 0 and D1D0 = XX (Run fo

r at least four clock cycles)

ii.

Enable =1, and D1D0 = 00 (Run for at least four clock cycles)

iii.

Enable = 1 and D1D0 = 10 (Run for at least four clock cycles)

iv.

Enable =1 and D1D0 = XX and Asynchronous Reset = 1 (assuming Reset is active high)

(Run for at least four clock cycles)

Enable Load Clock Asynchronous Reset Enable Load Clock Asynchronous Reset

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts