Question: Using the ALU description in chapter 4 ( along with the lecture slides ) , design, code, and test a 4 - bit ALU that

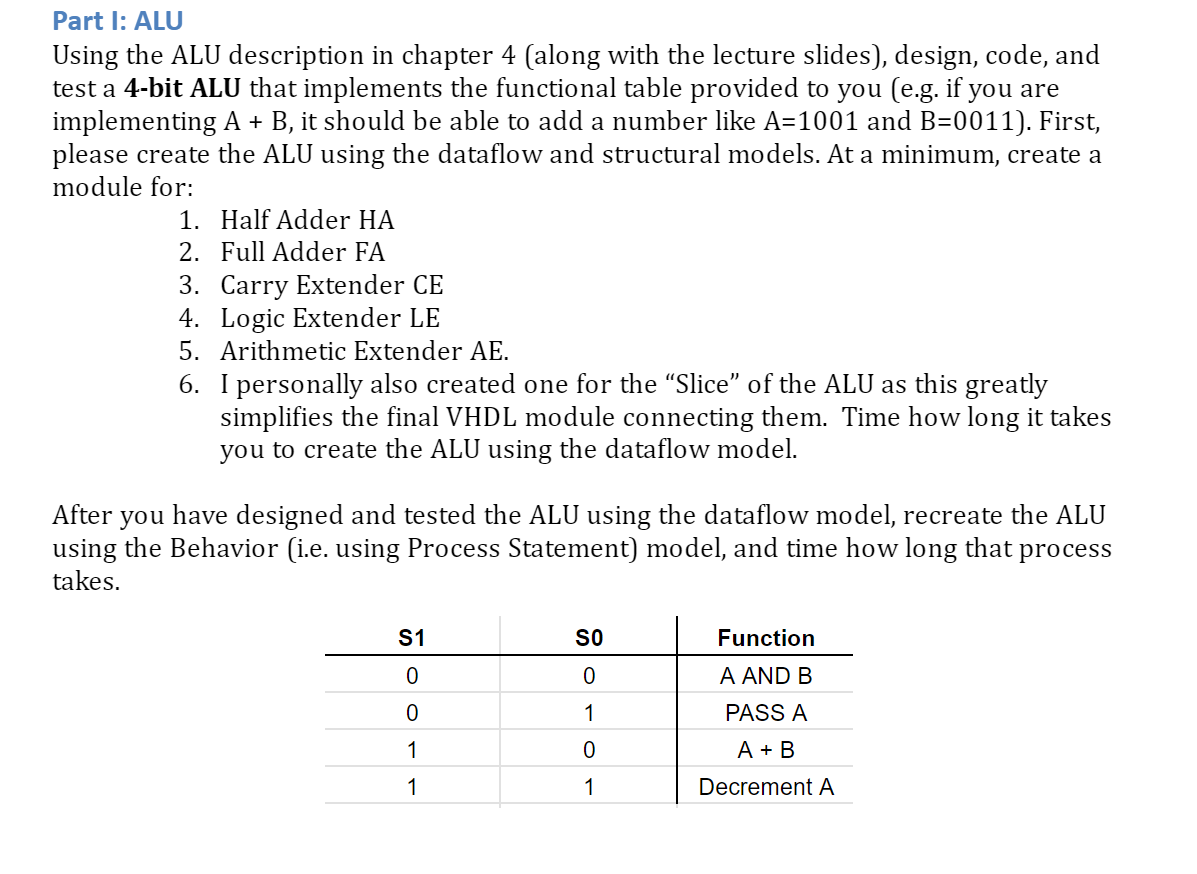

Using the ALU description in chapter along with the lecture slides design, code, and test a bit ALU that implements the functional table provided to you eg if you are implementing A B it should be able to add a number like A and B First, please create the ALU using the dataflow and structural models. At a minimum, create a module for:

Half Adder HA

Full Adder FA

Carry Extender CE

Logic Extender LE

Arithmetic Extender AE

I personally also created one for the "Slice" of the ALU as this greatly

simplifies the final VHDL module connecting them. Time how long it takes you to create the ALU using the dataflow model.

After you have designed and tested the ALU using the dataflow model, recreate the ALU using the Behavior ie using Process Statement model, and time how long that process takes.

Please use Xilinx Vivado in VHDL Thank you!

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock