Question: V. For this problem assume a cache is organized as follows: . 32 bit machine with 32 bit load and stores . 212 indexes .

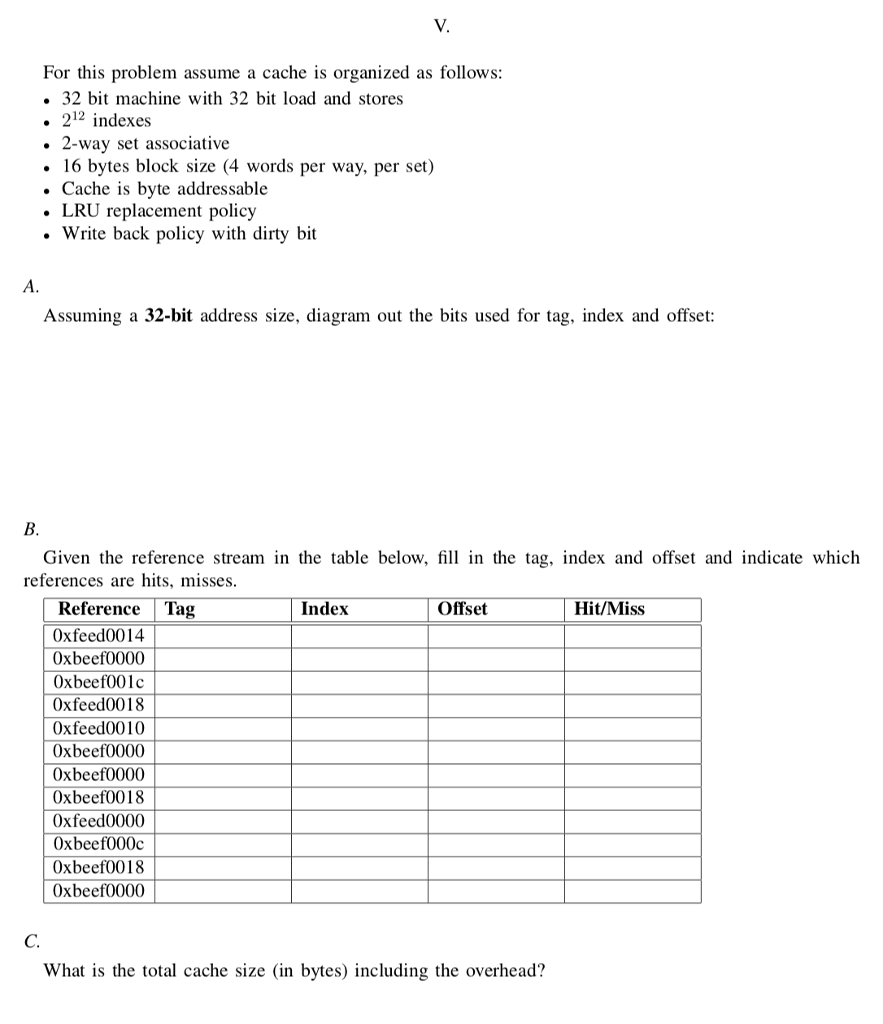

V. For this problem assume a cache is organized as follows: . 32 bit machine with 32 bit load and stores . 212 indexes . 2-way set associative 16 bytes block size (4 words per way, per set) Cache is byte addressable . LRU replacement policy . Write back policy with dirty bit Assuming a 32-bit address size, diagram out the bits used for tag, index and offset: Given the reference stream in the table below, fill in the tag, index and offset and indicate which references are hits, misse:s Index Offset Reference Tag Oxfeed0014 0xbeef0000 0xbeef001c Oxfeed0018 Oxfeed0010 Oxbeef0000 0xbeef0000 0xbeef0018 Oxfeed0000 Oxbeef000c Oxbeef0018 Oxbeef0000 Hit/Miss C. What is the total cache size (in bytes) including the overhead

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts