Question: We compared separated instruction and cache with unified cache. You may want to study the example on page B-16 first. The method in the example

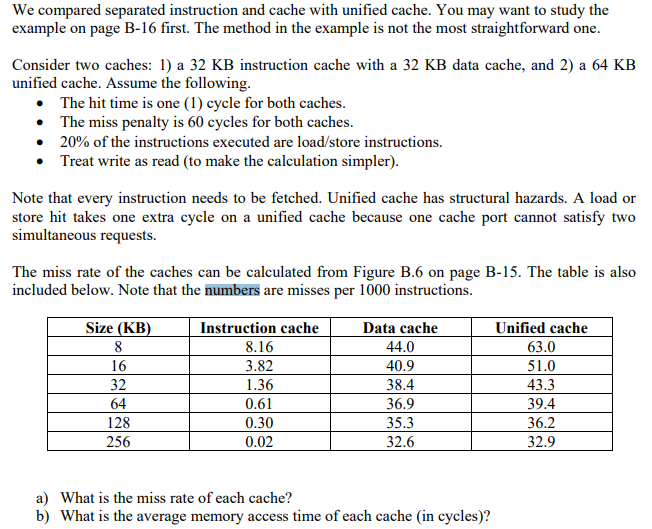

We compared separated instruction and cache with unified cache. You may want to study the example on page B-16 first. The method in the example is not the most straightforward one Consider two caches: 1) a 32 KB instruction cache with a 32 KB data cache, and 2) a 64 KB unified cache. Assume the following The hit time is one (1) cycle for both caches The miss penalty is 60 cycles for both caches. 20% of the instructions executed are load/store instructions. Treat write as read (to make the calculation simpler) Note that every instruction needs to be fetched. Unified cache has structural hazards. A load or store hit takes one extra cycle on a unified cache because one cache port cannot satisfy two simultaneous requests. The miss rate of the caches can be calculated from Figure B.6 on page B-15. The table is also included below. Note that the numbers are misses per 1000 instructions Size (KB) 32 64 128 256 Instruction cache 8.16 3.82 1.36 0.61 0.30 0.02 Data cache 44.0 40.9 38.4 36.9 35.3 32.6 Unified cache 63.0 51.0 43.3 39.4 36.2 32.9 a) What is the miss rate of each cache? b) What is the average memory access time of each cache (in cycles)? We compared separated instruction and cache with unified cache. You may want to study the example on page B-16 first. The method in the example is not the most straightforward one Consider two caches: 1) a 32 KB instruction cache with a 32 KB data cache, and 2) a 64 KB unified cache. Assume the following The hit time is one (1) cycle for both caches The miss penalty is 60 cycles for both caches. 20% of the instructions executed are load/store instructions. Treat write as read (to make the calculation simpler) Note that every instruction needs to be fetched. Unified cache has structural hazards. A load or store hit takes one extra cycle on a unified cache because one cache port cannot satisfy two simultaneous requests. The miss rate of the caches can be calculated from Figure B.6 on page B-15. The table is also included below. Note that the numbers are misses per 1000 instructions Size (KB) 32 64 128 256 Instruction cache 8.16 3.82 1.36 0.61 0.30 0.02 Data cache 44.0 40.9 38.4 36.9 35.3 32.6 Unified cache 63.0 51.0 43.3 39.4 36.2 32.9 a) What is the miss rate of each cache? b) What is the average memory access time of each cache (in cycles)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts