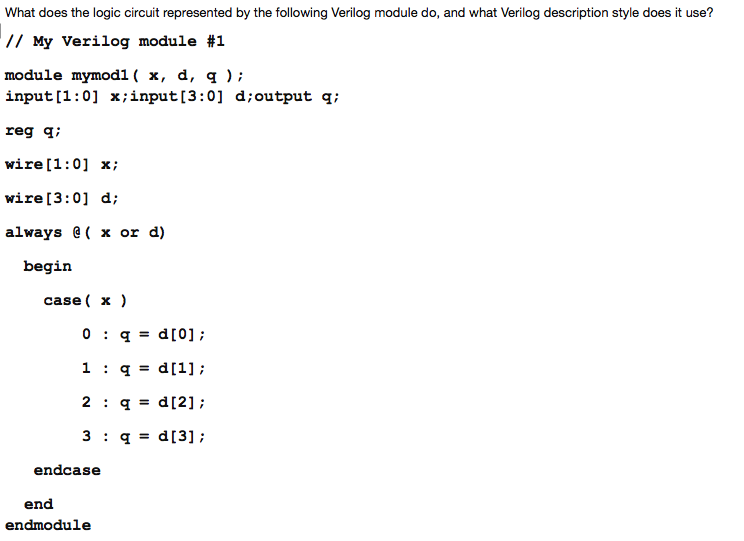

Question: why its 4-to-1 mux behavioral? What does the logic circuit represented by the following Verilog module do, and what Verilog description style does it use?

why its 4-to-1 mux behavioral?

What does the logic circuit represented by the following Verilog module do, and what Verilog description style does it use? // My Verilog module #1 module mymodl ( x, d, q) input[1:0] x;input[3:0] d;output q; reg q; wire [1:0] x; wire [3:0] d; always ( x or d) begin case ( x ) 1 : q=d[1]; 2 : g=d[2]; 3 q d[3]; endcase end endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts