Question: Will give you immediate thumbs up. Thanks Comp Arch question. Consider 10-stage pipeline IF1 IF2 ID1 ID2 EX1 EX2 MEMI MEM2 WB1 WB2 Consider Each

Will give you immediate thumbs up.

Thanks

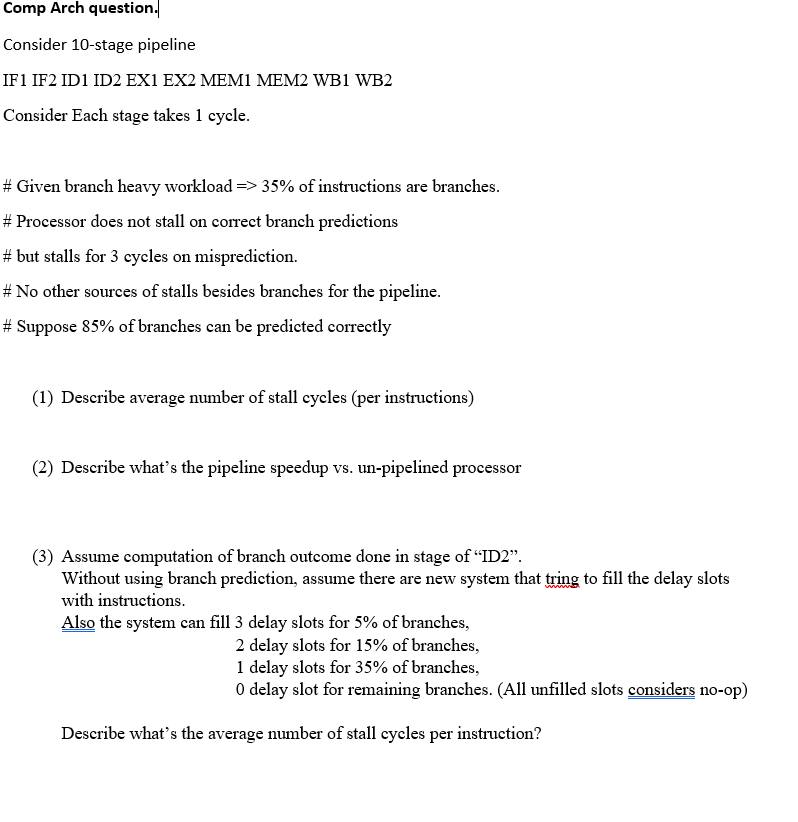

Comp Arch question. Consider 10-stage pipeline IF1 IF2 ID1 ID2 EX1 EX2 MEMI MEM2 WB1 WB2 Consider Each stage takes 1 cycle. #Given branch heavy workload => 35% of instructions are branches. # Processor does not stall on correct branch predictions # but stalls for 3 cycles on misprediction. # No other sources of stalls besides branches for the pipeline. # Suppose 85% of branches can be predicted correctly (1) Describe average number of stall cycles (per instructions) (2) Describe what's the pipeline speedup vs. un-pipelined processor (3) Assume computation of branch outcome done in stage of ID2. Without using branch prediction, assume there are new system that tring to fill the delay slots with instructions. Also the system can fill 3 delay slots for 5% of branches, 2 delay slots for 15% of branches, 1 delay slots for 35% of branches, 0 delay slot for remaining branches. (All unfilled slots considers no-op) Describe what's the average number of stall cycles per instruction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts