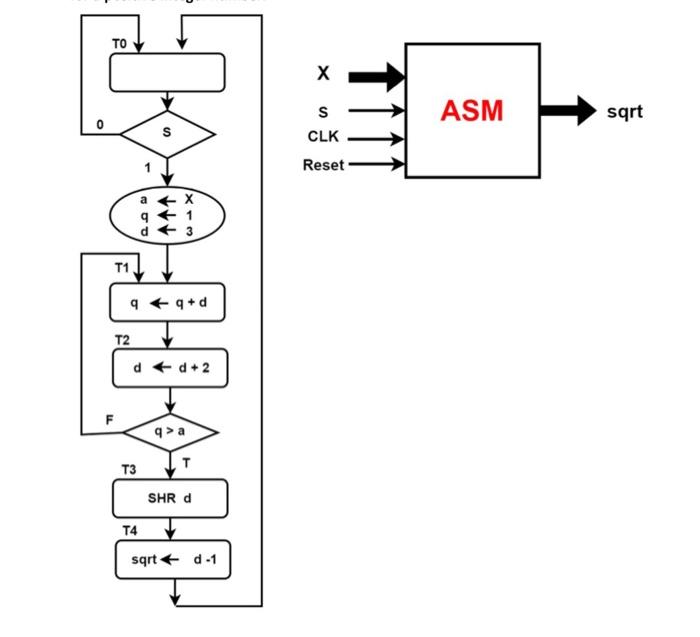

Question: write a complete verilog code Write a complete VERILOG code to implement the ASM chart using 3 procedural blocks. (Use a positive edge CLK and

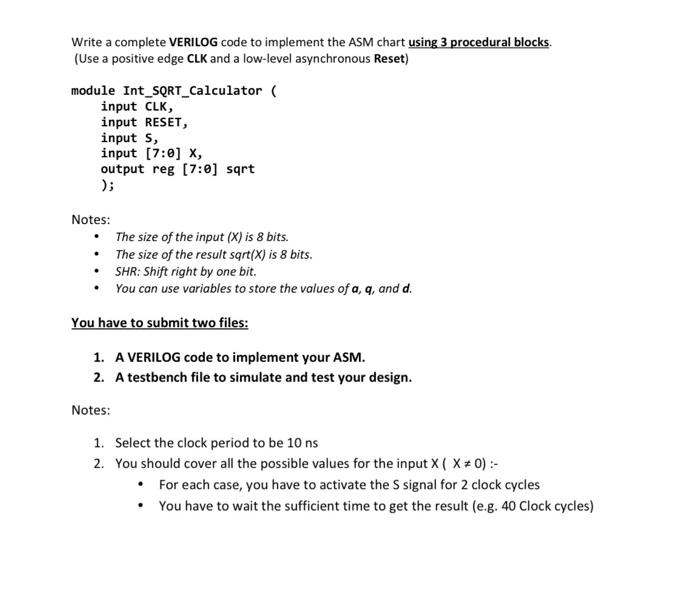

Write a complete VERILOG code to implement the ASM chart using 3 procedural blocks. (Use a positive edge CLK and a low-level asynchronous Reset) module Int_SQRT_Calculator ( input CLK, input RESET, input S, input [7:0] x, output reg [7:] sqrt ); Notes: - The size of the input (X) is 8 bits. - The size of the result sqrt( X ) is 8 bits. - SHR: Shift right by one bit. - You can use variables to store the values of a,q, and d. You have to submit two files: 1. A VERILOG code to implement your ASM. 2. A testbench file to simulate and test your design. Notes: 1. Select the clock period to be 10ns 2. You should cover all the possible values for the input X(X=0) :- - For each case, you have to activate the S signal for 2 clock cycles - You have to wait the sufficient time to get the result (e.g. 40 Clock cycles)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts